硬件电路时序计算方法与应用实例

其中,状态类信号是单端LVTTL信号,接收端利用TSCLK的上升沿对TSTAT[1:0]采样,方向为从物理层芯片发往链路层芯片;数据类信号是差分LVDS信号,接收端利用TDCLK的上升沿与下降沿对TDAT[15:0]和TCTL采样,即一个时钟周期进行两次采样,方向为从链路层芯片发往物理层芯片。

本文引用地址://www.cazqn.com/article/266060.htm由于接收信号组与发送信号组的时序分析类似,因此本文仅对发送信号组进行时序分析。

在本设计中,采用Vitesee公司的VSC9128作为链路层芯片,VSC7323作为物理层芯片,以下参数分别从这两个芯片的Datasheet中提取出来。

● 状态类信号的时序分析

对状态类信号,信号的流向是从物理层芯片发送到链路层芯片。

第一步,确定信号工作频率,对状态类信号,本设计设定其工作频率和时钟周期为:

Freq=78.125MHz;

Tcycle = 1/ Freq = 12.8ns;

第二步,从发送端,即物理层芯片手册提取以下参数[3]:

-1ns < Tco < 2.5ns;

第三步,从接收端,即链路层芯片手册提取建立时间和保持时间的要求[4]:

Tsetup(min) = 2ns;

Thold(min) = 0.5ns;

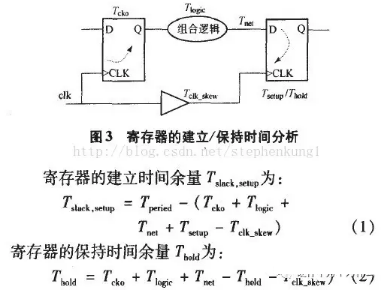

将以上数据代入式1和式2:

2.5ns + (Tflight-data - T flight-clk)MAX + 2ns < 12.8ns

-1ns + (Tflight-data - T flight-clk)MIN > 0.5ns 整理得到:

1.5ns < (Tflight-data - T flight-clk) < 8.3ns

基于以上结论,同时考虑到Vsig = 6inch/ns,可以得到如下结论,当数据信号和时钟信号走线长度关系满足以下关系时,状态类信号的时序要求将得到满足:TSTAT信号走线长度比TSCLK长9英寸,但最多不能超过49.8英寸。

● 数据类信号的时序分析

对数据类信号,信号的流向是从链路层芯片发送到物理层芯片。

第一步,确定信号工作频率,对数据类信号,本设计设定其工作频率为:

Freq=414.72MHz;

与状态类信号不同的是,数据类信号是双边沿采样,即,一个时钟周期对应两次采样,因此采样周期为时钟周期的一半。采样周期计算方法为:

Tsample = ½*Tcycle = 1.2ns;

第二步,从发送端,即链路层芯片手册提取以下参数[4]:

-0.28ns < Tco < 0.28ns;

第三步,从接收端,即物理层芯片资料可以提取如下需求[3]:

Tsetup(min) = 0.17ns;

Thold(min) = 0.21ns;

将以上数据代入式1和式2,需特别注意的是,对数据类信号,由于是双边沿采样,应采用Tsample代替式1中的Tcycle:

0.28ns + (Tflight-data - T flight-clk)MAX + 0.17ns < 1.2ns

-0.28ns + (Tflight-data - T flight-clk)MIN > 0.21ns

整理得到:

0.49ns < (Tflight-data - T flight-clk) < 0.75ns

基于以上结论,同时考虑到Vsig = 6inch/ns,可以得到如下结论,当数据信号和时钟信号走线长度关系满足以下关系时,数据类信号的时序要求将得到满足:TDAT、TCTL信号走线长度比TDCLK长2.94英寸,但最多不能超过4.5英寸。

5 结论

高速电路中的时序设计,虽然看似复杂,然而只要明晰其分析方法,问题可以迎刃而解。

参考文献:

[1] 王剑宇. 高速电路设计实践[M]. 电子工业出版社,2010:131

[2] Optical Internetworking Forum. Implementation Agreement: OIF-SPI4-02.0[J]. OIF,2002:1-5

[3] Vitesse. VSC7323 Datasheet[J]. Vitesse,2006: 306~312

[4] Vitesse. VSC9125 and VSC9128 Datasheet[J]. Vitesse,2006:769-772

评论