实验一:一位半加器

1. 实验目的

2. 实验任务

设计一个1位半加器电路,然后在实验板上实现自己设计的逻辑电路,并验证是否正确。

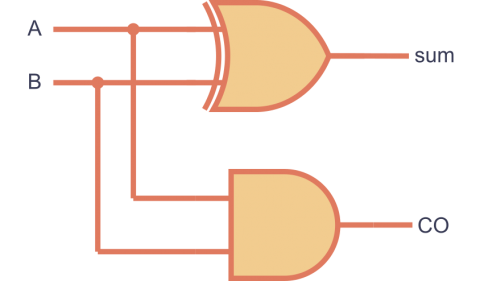

加法器是逻辑运算电路中最基础的组成单元。将如果不考虑有来自低位的进位, 将两个二进制数相加, 称为半加, 实现半加的电路叫做半加器。1位半加器每次对两个1位的二级制数进行相加。按照二进制加法运算规则, 可以得到如下表4-1所示的半加器真值表。

sum = A’B + AB’ = A⊕B

CO = AB

程序清单halfadder.v

module halfadder ( input A, //第一个加数a input B, //第二个加数b output sum, //a与b的加和 output co //a与b的进位 ); xor (sum, A, B) ; //门电路XOR (输出, 输入1, 输入2) and (co, A, B) ; //门电路AND (输出, 输入1, 输入2) endmodule

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。