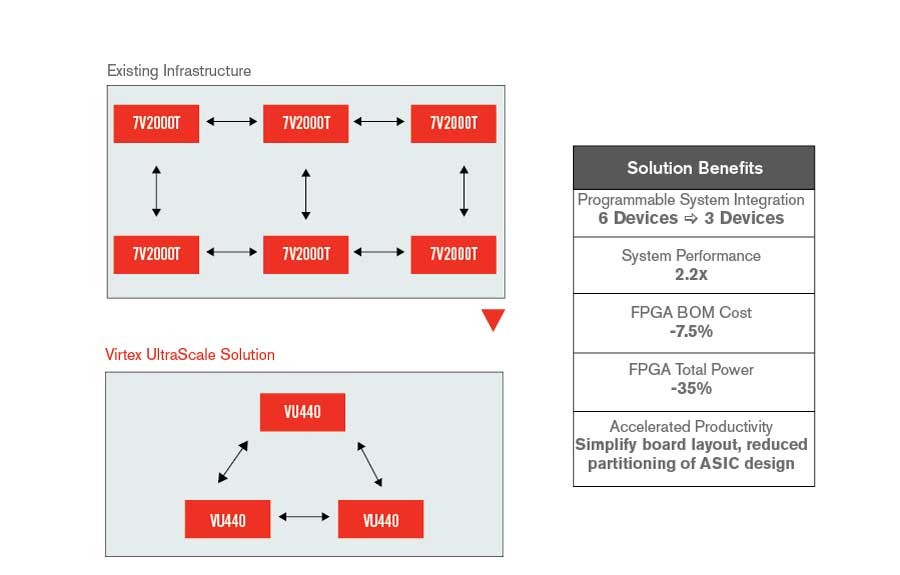

使用 Xilinx UltraScale™ 架构,ASIC 原型 & 仿真可实现突破性性能和集成。 Virtex® UltraScale 器件通过高逻辑容量、超过 90% 器件利用率、堪比 ASIC 的时钟、增强型布线和面向引脚多路复用的高速收发器简化设计分区。突破性架构融合 Xilinx Vivado® Design Suite 为满足领先的 ASIC 和 SoC 平台需求提供了理想的解决方案。

解决方案概述与优势

● 突破性器件容量 降低分区数量,并简化开发板布局

● Vivado Design Suite 增强型布线和协同优化确保超过 90% 的器件利用率

● 堪比 ASIC 的时钟性能 有效地映射复杂的 ASIC 和 SoC 时钟树

● 高速收发器 实现 FPGA 之间高效的引脚多路复用,并支持下一代系统的 I/O 接口需求

UltraScale 架构优势

● 海量 I/O 带宽

● 提供 > 1 Tbps 芯片至芯片带宽

● 低延时收发器实现芯片间互连

● 海量数据流 & 布线

● 支持高性能的本地 ASIC 总线

● 堪比 ASIC 的时钟性能

● 最大化复杂 SoC 原型的灵活性

● 系统性能

● 单器件性能提升 15-30 %

● 分区减少,性能提升 3 倍

● 功耗管理

● 系统功耗最多可以降低 35%