低触发电压可控硅结构静电防护器件

导语:

可控硅SCR(Silicon Controlled Rectifier)结构静电防护器件由于其自身的正反馈机制,具有单位面积泄放电流高、导通电阻小、鲁棒性强、防护级别高的优点,但同时它还引入了触发电压高响应速度慢、维持电压低易闩锁的缺点。本文介绍可控硅结构静电防护器件降低触发电压提高开启速度的方法。

正文:

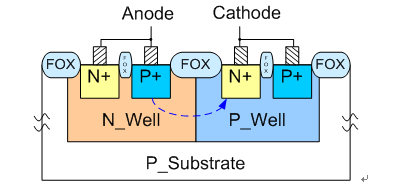

可控硅器件能够以较小的版图面积获得较高ESD防护等级,因此,此类器件已在集成电路片上静电防护中占有一席之地。但是在深亚微米CMOS工艺中SCR器件仍然具有高的开启电压的缺点,触发电压一般高于20V,且高于输入级的栅氧化层击穿电压。随着工艺水平的不断进步,栅氧化层的厚度不断减小,击穿电压进一步降低,因此,避免内核电路薄栅氧化层器件永久损坏的必要措施是减小SCR器件开启电压提高开启速度。如图1所示为简单横向SCR器件剖面图,针对此结构降低触发电压的器件结构有MLSCR和LVTSCR;针对此结构提高开启速度的一般方法是采用辅助触发电路,例如,栅极耦合技术、热载流子触发技术、衬底触发技术、双触发技术等。本文介绍几种降低触发电压提高开启速度的方法。

图1 简单横向SCR器件剖面图

1、改进型SCR(Modified Lateral SCR,MLSCR)

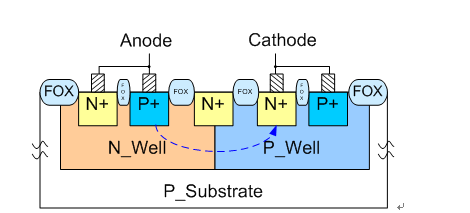

如图2所示,MLSCR通过在N阱/P阱的结面上增加N+扩散区来降低此结的雪崩击穿电压。通过此法可将开启电压降低到12V,但还不足以保护输入级的薄栅氧化层,因此,MLSCR与LSCR一样需要与二级保护器件配合来实现输入级的静电保护。当然,由于其开启电压的降低,二级保护器件的版图面积可以减小。而对于输出级,由于两级ESD保护会给正常工作下的电路带来信号延时,LSCR和MLSCR一般不用于输出级的静电保护。

图2 MLSCR器件剖面图

2、低触发电压SCR(Low-Voltage Triggering SCR,LVTSCR)

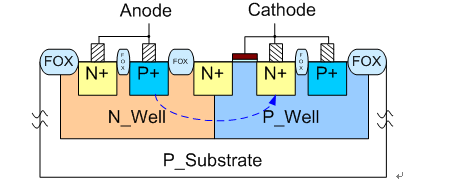

如图3所示,LVTSCR通过在结构中嵌入一个NMOS将器件开启电压降低到约7V,与短沟NMOS的漏击穿电压或穿通电压相近。此器件可独立使用作为CMOS集成电路的输入级ESD保护,极大地减小了ESD保护电路的版图实现面积。而作为输出级保护时,需要在LVTSCR和输出级之间加入小的串联电阻以保证ESD保护的有效性。

图3 LVTSCR器件剖面图

3、栅极耦合的LVTSCR(Gate-Coupled LVTSCR)

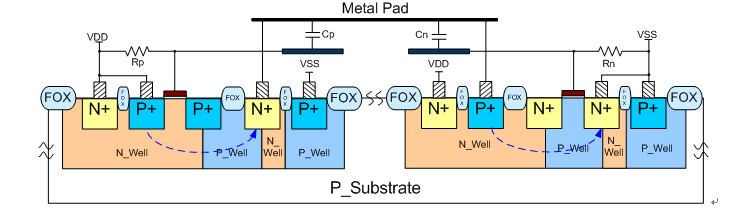

如图4所示为互补型栅极耦合LVTSCR,此器件采用非雪崩击穿机制来开启。通过合理设置Cn和Cp的电容值,可以使耦合到栅上的电压在电路正常工作状态下小于内嵌NMOS/PMOS的阈值电压,而在ESD应力到来时大于内嵌NMOS/PMOS的阈值电压。LVTSCR的开启电压可以通过调整内嵌NMOS/PMOS栅极的耦合电压来设置。耦合电压越大,LVTSCR的开启电压越低,快速开启的LVTSCR可有效保护输入/输出级。

图4 栅极耦合的 LVTSCR器件结构

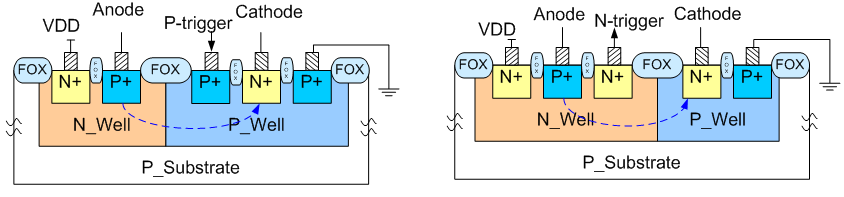

4、衬底触发SCR(Substrate-Triggered SCR,STSCR)

如图5所示为P型和N型衬底触发SCR器件,它们分别通过在传统LSCR器件中加入P+或N+扩散区作为触发节点。衬底触发SCR器件的开启机制属于电流触发事件。当电流被加在SCR器件的衬底,也即寄生三极管的基极时,SCR可以快速触发并进入闩锁状态。随着衬底触发电流的增大,开启电压下降、开启时间缩短。当然,此器件的应用需要外加RC侦测电路。

图5 衬底触发的SCR器件结构

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。