新闻中心

在Zynq上用MIG扩展内存(2)-Vivado篇

- 来源:Xilinx

- 发布时间:[2014-01-29]

硬件平台:ZC706开发板

软件工具:Vivado 2013.2

Step 1: 创建工程

启动Vivado 2013.2,创建一个新的工程zc706_mig。选中Create project subdirectory。

选择RTL Project

一路Next,在Default Part页面选择ZC706开发板。

Step 2: 配置Zynq

在左面的Flow Navigator窗口,单击Create Block Design,Design Name填写zynq。

在Diagram Tab页里面添加IP ‘ZYNQ7 Processing System’。

双击processing_system7_1,打开配置界面。取消所有外设,仅仅保留UART。UART1使用MIO 48..49。关闭FCLK_CLK0的输出。

Step 3: 配置MIG

在Diagram Tab页里面添加IP ‘MIG 7 Series’。双击mig_7series_1,打开配置界面。

在Memory Selection页,选择DDR3

在Controller Options也,配置Clock Period为1250ps,配置Memory Type=SODIMMS; Memory Part=MT8JTF12864HZ-1G6。

在AXI Parameter页,配置Data Width=32, ID width=12。

在Memory Options页,配置Input Clock Period=5000ps(200MHz).

在FPGA Options页,配置System Clock=Differential,Reference Clock=Use System Clock,System Reset Polarity=ACTIVE HIGH。

在Extended FPGA Options页,选中DCI Cascade。

在IO Planning Options页,选择Fixed Pin Out,然后导入labfiles\zc706_mig_pinout.ucf,单击Validate,忽略warnings,单击Next。

在System Signals Selection页,单击Next。

在Summary页,单击Next。

在Simulation Options页,选择Accept,单击Next。

在PCB Information页,单击Next。

在Design Notes页,单击Generate。

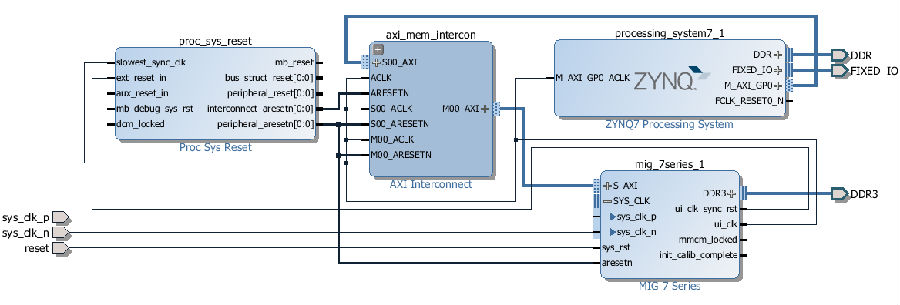

Step 4: 建立IP之间的连接

在Diagram Tab页, 单击窗口上部的Run Connection Automation,选择/mig_7series_1/S_AXI,系统将自动添加IP并建立部分连接。

单击窗口上部的Run Connection Automation,选择/mig_7series_1/sys_rst。

连接/mig_7series_1/ui_clk到processing_system7_1/M_AXI_GP0_ACLK

连接/mig_7series_1/aresetn到/proc_sys_rest/peripheral_aresetn[0:0]

单击窗口上部的Run Block Automation,选择processing_system7_1

单击/mig_7series_1/SYS_CLK前面的加号,展开这个接口。

选中/mig_7series_1/sys_clk_p,单击右键,选择Create Port。在弹出的窗口里面更改Type为Clock,填写Frequency(MHz)为200。

对/mig_7series_1/sys_clk_n执行同样的操作。

选中/mig_7series_1/DDR3接口,单击右键,选择Make External

单击Diagram Tab页左边最下面的Regenerate Layout按钮,由工具自动重新排布。生成的结果如下。是不是感觉非常漂亮?

Step 5: 创建约束

命名为system,将以下内容拷贝到约束文件中:

set_property LOC G9 [ get_ports sys_clk_n]

set_property IOSTANDARD DIFF_SSTL15 [ get_ports sys_clk_n]

set_property LOC H9 [ get_ports sys_clk_p]

set_property IOSTANDARD DIFF_SSTL15 [ get_ports sys_clk_p]

set_property LOC A8 [ get_ports reset]

set_property IOSTANDARD LVCMOS15 [ get_ports reset]

# additional constraints

#

create_clock -name sys_clk_pin -period "5.0" [get_ports "sys_clk_p"]

Step 6:设计验证

在Block Design窗口里面,在zynq.bd上面单击右键,选择Generate Output Products,然后再单击右键,选择Create HDL Wrapper。

在左面的Flow Navigator窗口,单击Generate Bitstream。

在我的计算机上,大约20分钟后,bit文件生成。

然后在Vivado中,单击File->Export->Export Hardware for SDK,选中Launch SDK。

在SDK里面,可以用模板“Memory Tests”创建一个工程,测试确认MIG工作正常。

以此为基础,开发者可以灵活的调整MIG的AXI端口和Memory端口的工作频率,完成贴合自己应用的嵌入式设计。

最新活动

- 寻找《xilinx UltraScale™ MPSoC架构》 下载文档有奖

- 活动时间:2014/3/22-2014/5/22

- Xilinx Zynq交流群已开辟

- QQ群号:323470211,还有 Xilinx 资深工程师入驻,帮您答疑解惑!!!

- ZYNQ论坛互动专区

- ZedBoard及ZingBoard开发优秀手记展示,详情进入……