新闻中心

理由一:最有效的ARM+FPGA 分析和控制架构

- 来源:xilinx

- 发布时间:[2013-05-28]

理由一:最有效的ARM+FPGA 分析和控制架构

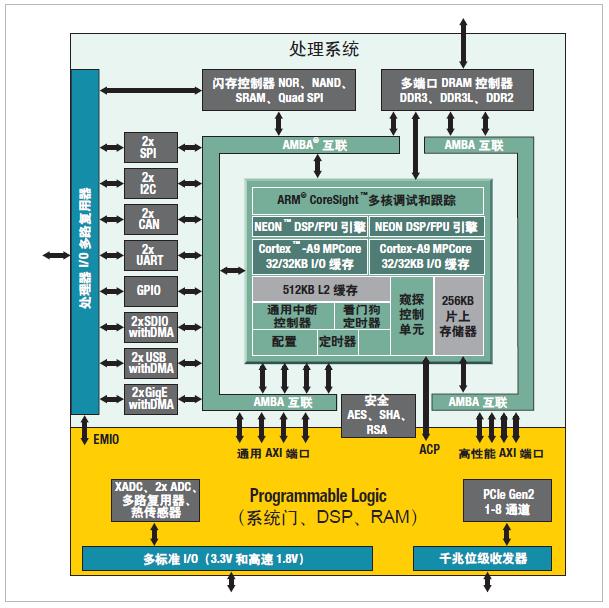

Zynq All Programmable SoC 的核心的是1GHz 双核硬化实现的ARM Cortex-A9 MPCore 微处理器。两个ARM 处理器通过基于ARM AMBA AXI 的互联机制与片上存储器、SDRAM 和闪存存储器控制器以及外设模块进行通信。总之,这些硬化模块构成了Zynq-7000 All Programmable SoC Processor System(PS)。

Zynq-7000 All Programmable SoC

片上PS 通过多个ARM AMBA AXI 端口连接到Zynq 器件的片上 Programmable Logic( PL),在 Zynq 架构的两大关键组件之间形成了极为高效的耦合。它们中间包括有2 个32位AXI 主接口、2 个32 位AXI 从接口、4 个64 位可配置缓冲型高性能AXI 从接口和1 个64 位AXI ACP(加速器一致性端口)接口。也就是说Zynq PS 和PL 之间共有9 个AXI 接口。ARM AXI PS-Pl 连接的数量和大小是一个关键的架构选择,需要认真考虑Zynq PS 的带宽要求。4 个64 位/32 位可配置高性能AXI 端口使得PL 能通过4 个独立的1kBFIFO 缓冲器直接高速访问Zynq-7000 All Programmable SoC 的片上存储器和SDRM 控制器。这样,Zynq PL 中实现的一些单独的硬件加速器就能独立高速访问基于Zynq 系统的主存储器。如果访问要与片上缓存相一致,那么PL 中实现的加速器可采用64 位ACP 连接,其直接连接到ARM Cortex-A9 MPCore 处理器的窥探控制单元。

除了64 位/32 位可配置AXI 端口之外,还有4 个32 位AXI 端口用于连接Zynq PS 和PL。这些端口在Zynq PS 和Zynq PL 实现的任何外设类IP 块之间提供连接。

最新活动

- 寻找《xilinx UltraScale™ MPSoC架构》 下载文档有奖

- 活动时间:2014/3/22-2014/5/22

- Xilinx Zynq交流群已开辟

- QQ群号:323470211,还有 Xilinx 资深工程师入驻,帮您答疑解惑!!!

- ZYNQ论坛互动专区

- ZedBoard及ZingBoard开发优秀手记展示,详情进入……