干货收藏:电路模块设计合集

一.电源部分

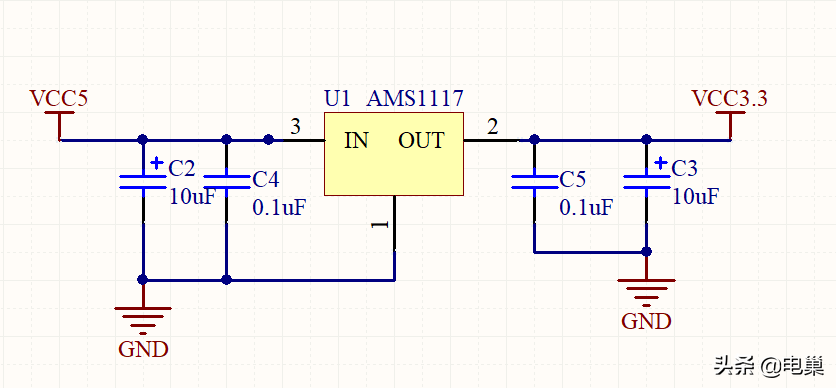

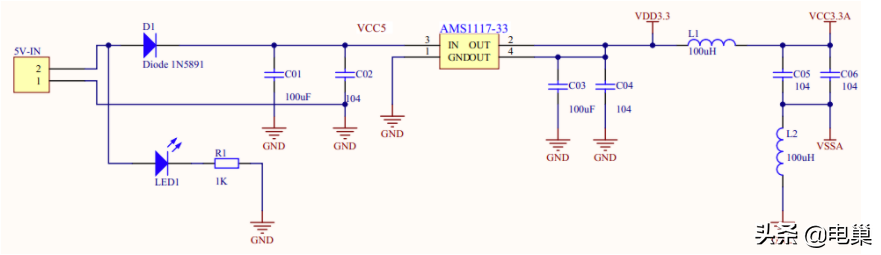

1. 5V转3.3V电路

常用IC: AMS1117 ;LD1086D2M33;HT78XX

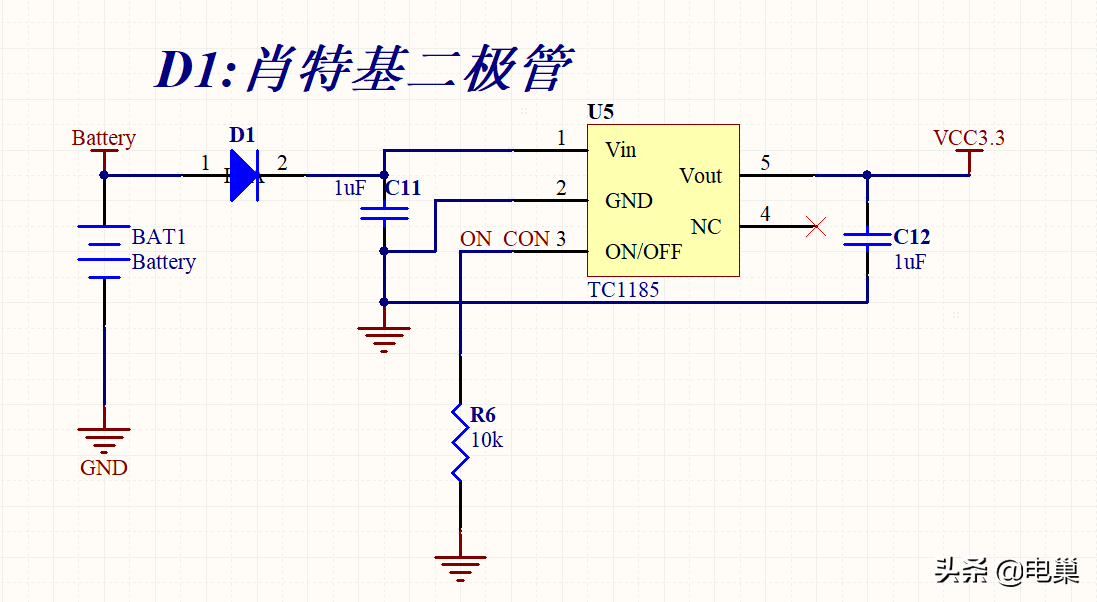

2. 3.7V(电池)转3.3V电路

常用IC(LDO): TC1185;

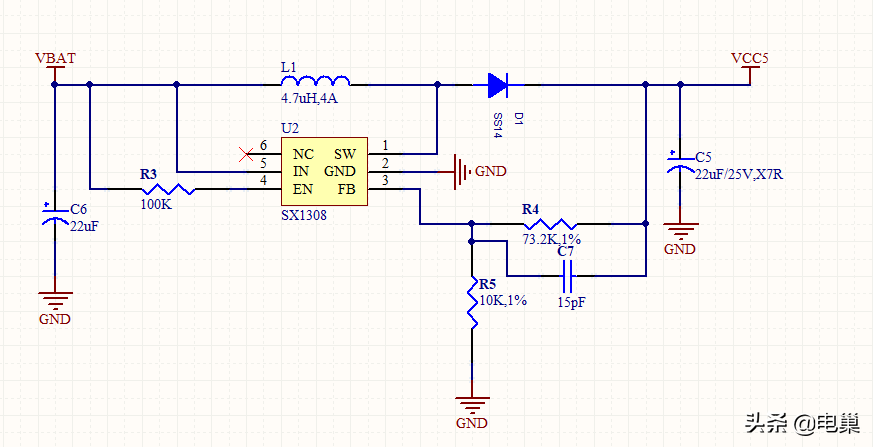

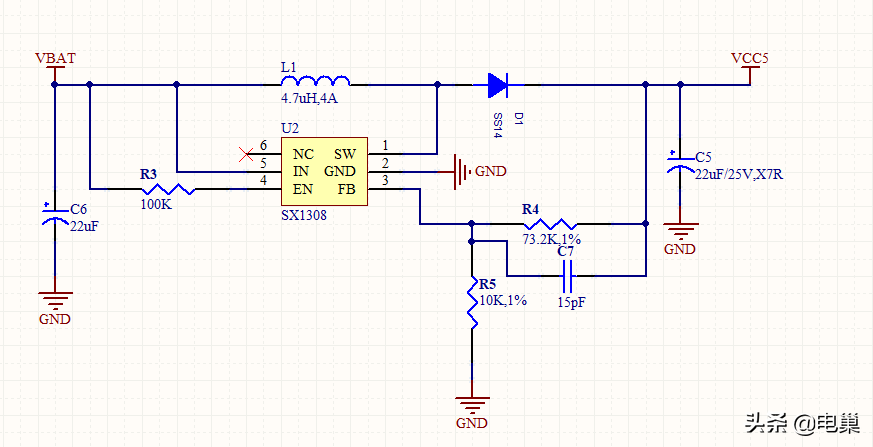

3.7V升压到5V

3. 系统上电控制电路

注: 电容并联滤波,去耦,一般并联值的关系为10倍;为了安全,常会串联一个保险管之类。

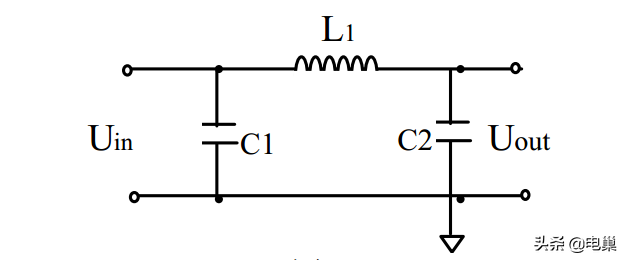

4. 输入侧电源的滤波

对于单板的电源输入侧, 出于上电特性及热插拔的需要, 需要加π型滤波电路。

其中, C1 为输入侧的输入电容, L 为输入电感, C2 为π型滤波电路的输出侧电容; C1 的主要目的是为了限制上电瞬间的电压上升率,并滤除输入侧电路由电源引入的纹波,因此, C1 一般是由直流电容及交流电容组成的并联电容组,其中直流电容的主要作用是去除电容中的纹波,而交流电容的主要作用是为了去耦。

从参数及器件选择上,输入侧一般选取钽电容,去耦电容的值为0.01uf ~1uf 之间,针式或贴片均可,但从生产工艺的角度,则以选取贴片为佳,推荐的参数为直流电容 10uf,交流电容 0.1uf。

电感的作用为抑制电流变化率,电感越大,抑制效果越好,但同时电感太大时的上电特性不好,上电及下电时,电感两端会产生反电势,这样会对后面的负载产生影响,故参数不宜过大,因而推荐的参数为 10uH。

输出侧的电容不仅要完成去耦及滤纹波的作用,而且还须维持滤波后电平不受电感反电势的影响, 兼顾考虑板内负载大小及板内其他去耦电容的数量, 推荐参数为直流电容 10uf,交流电容 0.01~1uf。

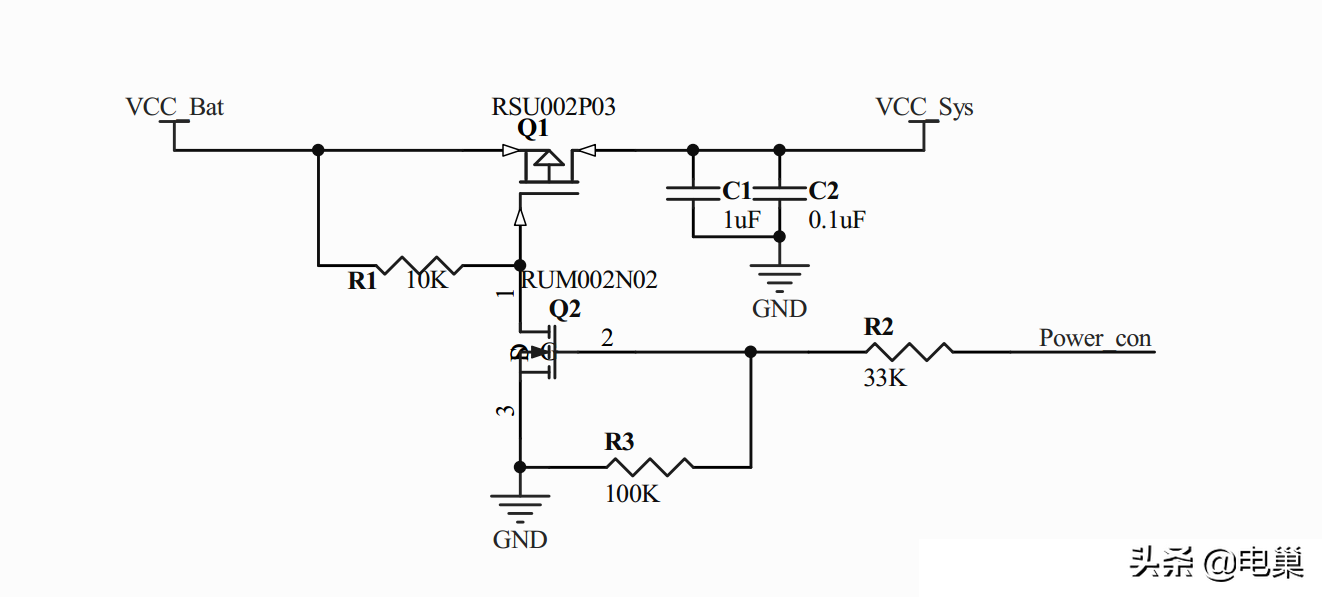

5. MOS开关上电控制电路

通过MCU的 IO 控制NMOS的开关,实现系统的上电。

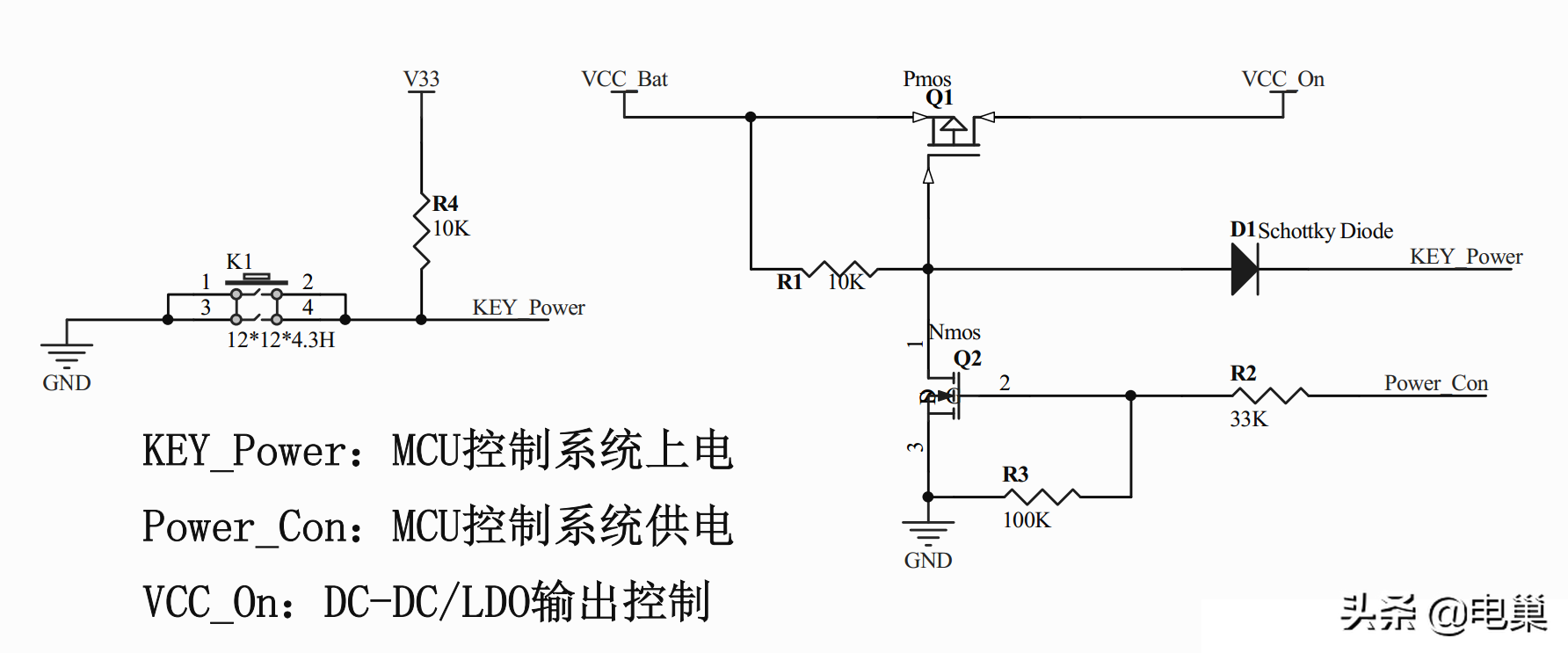

6. MOS开关上电、供电控制电路

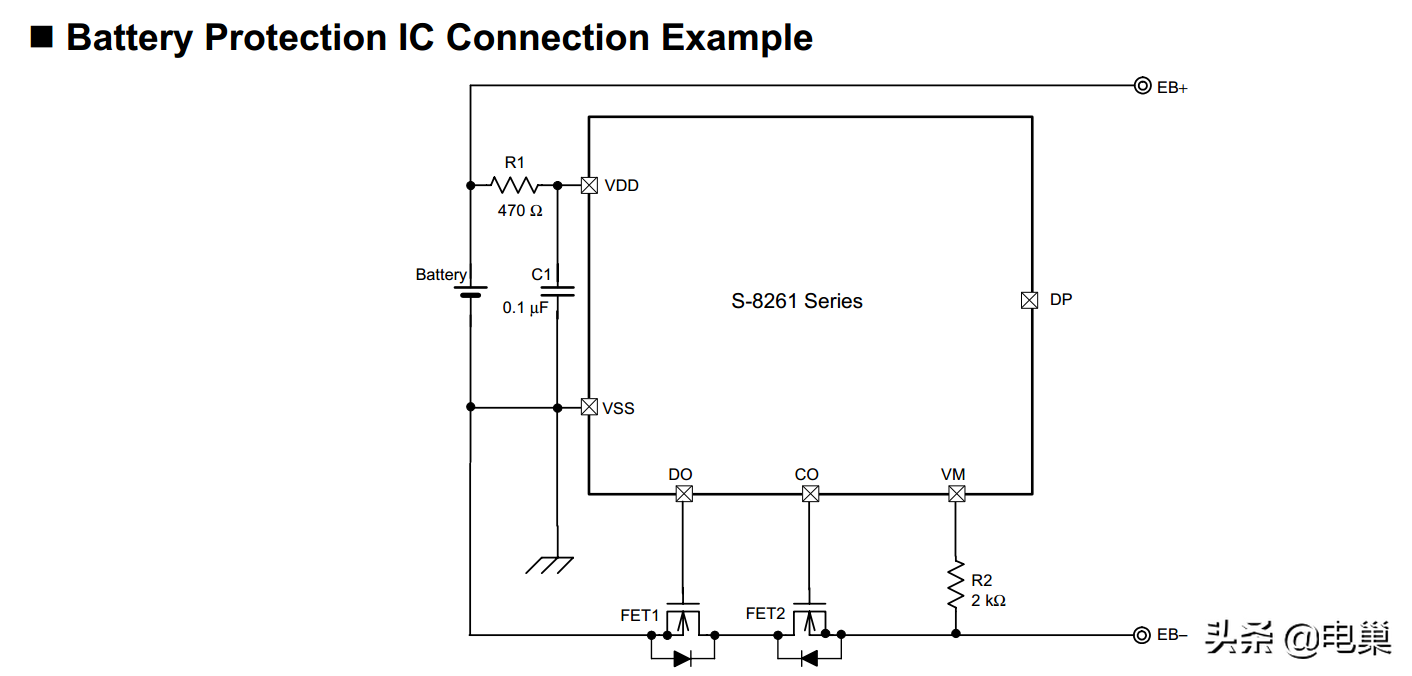

7. 锂电池保护电路

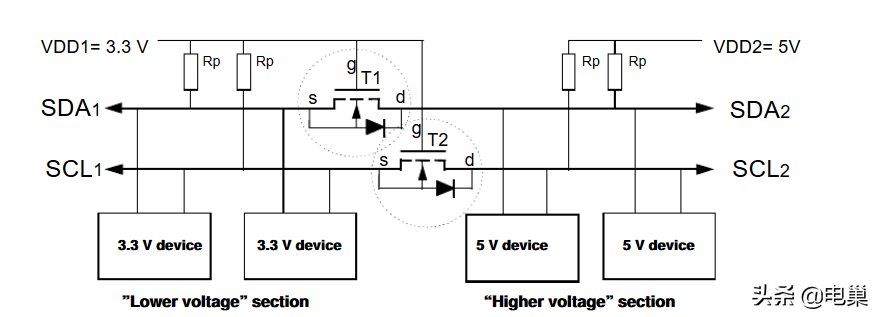

7.MOS控制电平转换电路

Bi-directional level shifter3.3与5v转换

二.调试工具

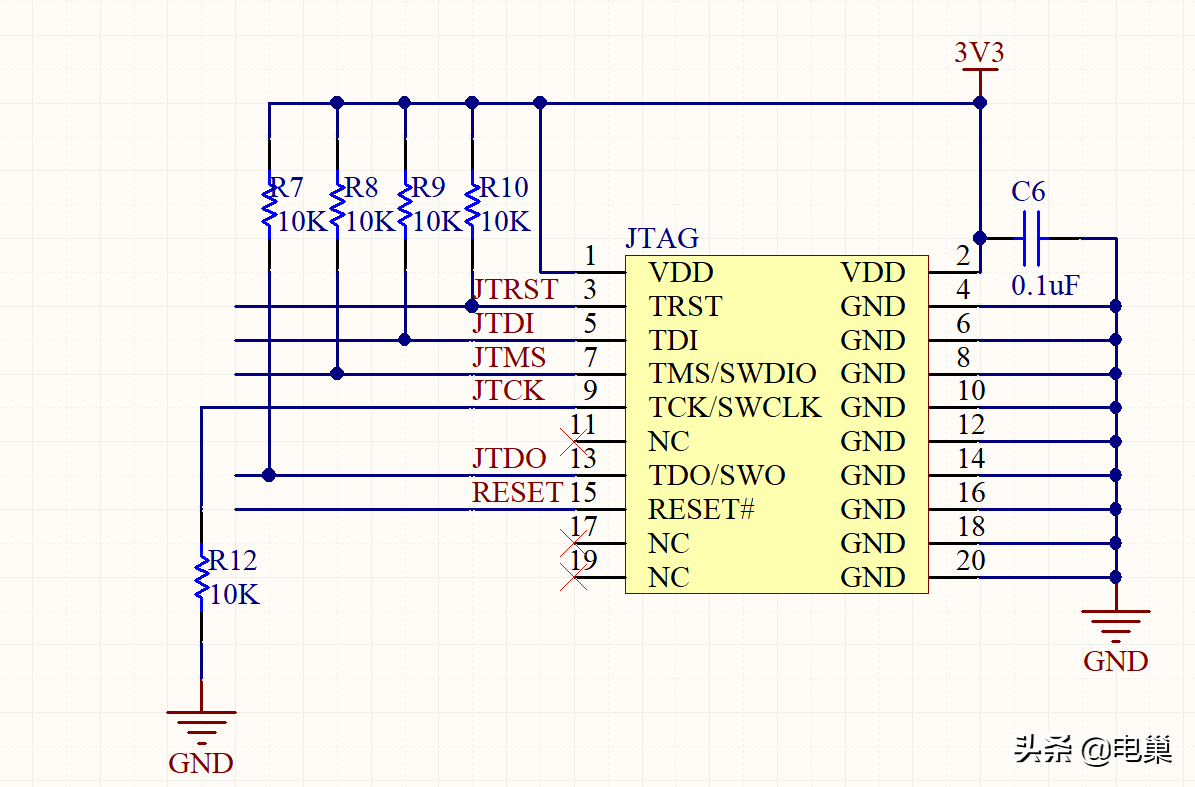

1. JTAG电路

注:VTREF)接口信号电平参考电压一般直接连接Vsupply。(比如3.3V还是5.0V)

三.外设

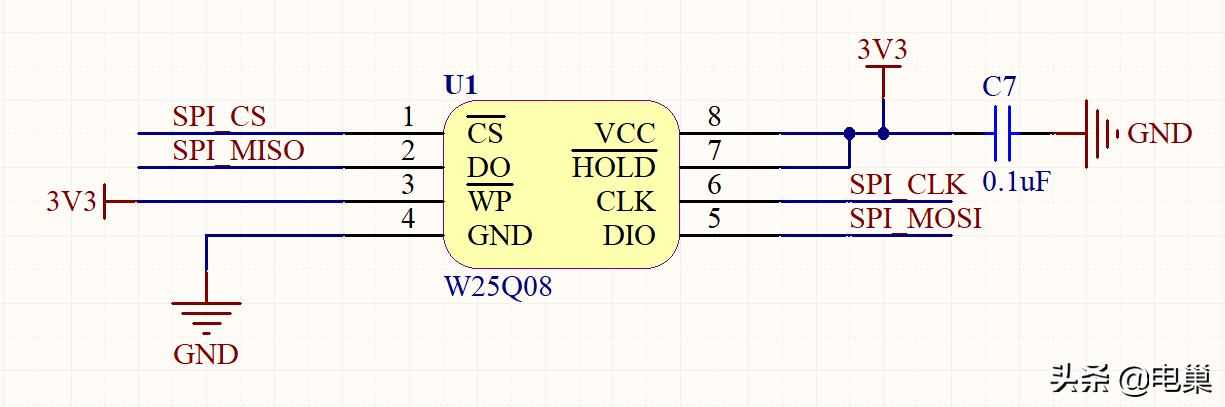

1.FLASH驱动电路

注: 信号线上上拉电阻的添加。

1·上拉电阻的选取原则:

A·提高灌电流的能力:

单板内部的器件功耗及驱动能力各不相同,这样在器件连接时的灌电流能力不尽相同,连接上会有驱动问题,此时需要加上拉电阻。

B·电平兼容:

板内或板间器件选取各不相同,信号电平特性各不相同,出于兼容性的考虑,须加上拉电阻以保证兼容性。

C·电平稳态的特性:

个别器件在上电时要求某些管脚的初始电平固定为高,此时必须加上拉电阻以保证器件能够正常的工作。

D·器件及参数选取:

对于 A, B,一般的上拉电阻选取 2K~1M 欧姆,视负载情况而定,重负载时电阻应选取靠近下限,轻负载时选取上限,这里的负载以器件功耗指标来确定;对于上述 C 的情况,则以该种器件的数据特性来决定。

器件一般以金属膜的电阻或阻排为准。

2·下拉电阻的选取原则:

A·电平兼容:

板内或板间器件选取各不相同,信号电平特性各不相同,出于兼容性的考虑,须加下拉电阻以保证兼容性。

B·端接:

板内或板间的信号频率较高或信号上升沿较陡时,需要加端接电阻下拉到地,一般此时经常性的会再串入一个适当的电容。

C·电平稳态特性:

个别器件在上电时要求某些管脚的初试电平固定为低,此时必须加下拉电阻以保证器件能够正常的工作。

D·器件及参数选取:

对于 A,下拉电阻一般选取 1K~100K 欧姆,视负载电平情况而定, CMOS 电平的负载,电阻应选取下限, TTL 电平时选取上限,这里的电平以负载指标来确定;对于上述 B 的情况,一般选取75~150 欧姆的电阻;对于上述 C 的情况,则以该种器件的数据特性来决定;器件一般以金属膜的电阻或阻排为准。

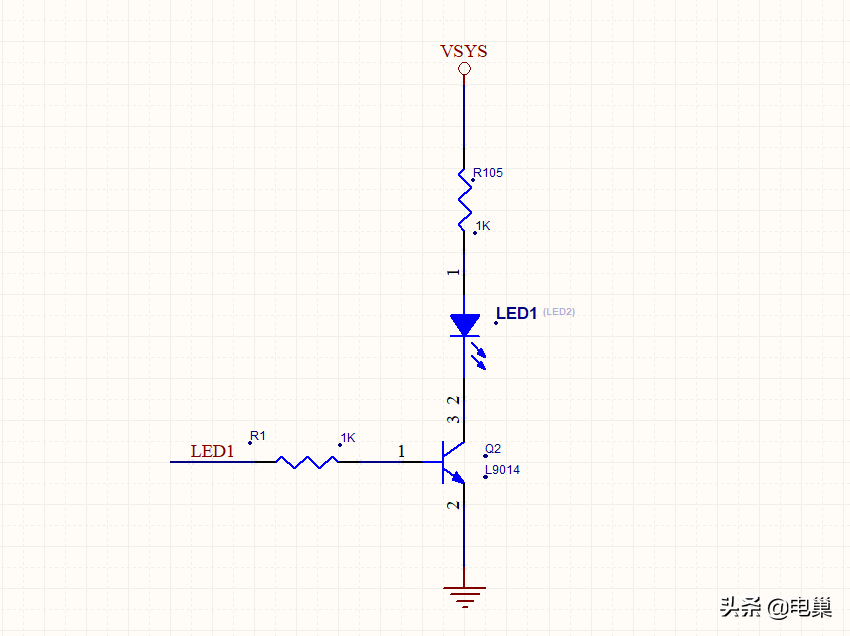

2.LED三极管驱动电路

评论