无线红外传输设计技术(08-100)

红外无线是计算机与外设的一种常用连接技术。本文介绍红外编/译码器与主控机和光收发器的连接设计。

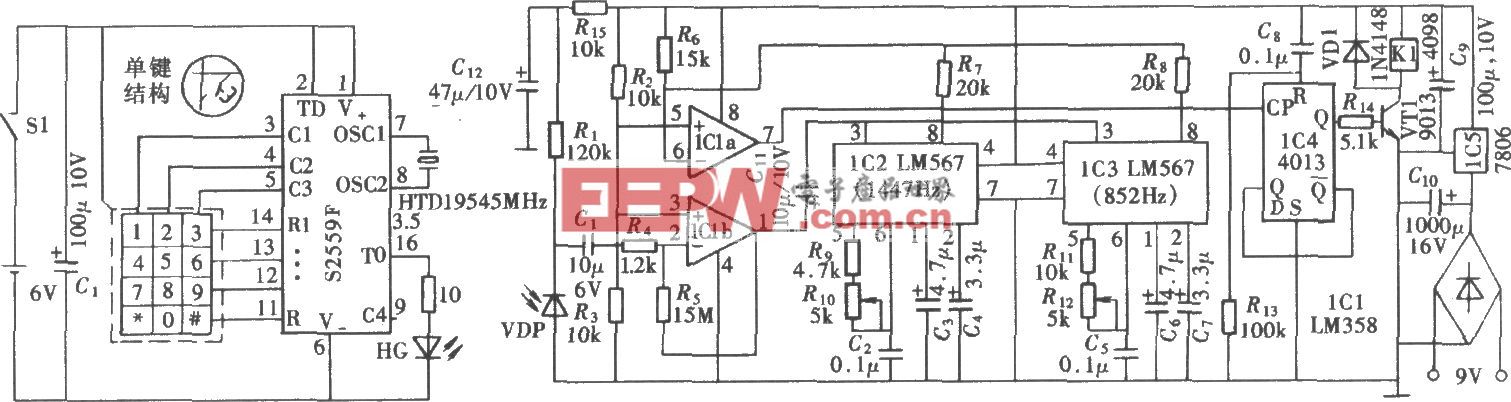

本文引用地址://www.cazqn.com/article/91750.htmMCP2122是一款IrDA标准编/译码器。它有两个接口:主机UART接口与IR接口(图1),前者与发送与接收数据的主控器接口;后者连接至光收发电路,将电脉冲转换为红外光(编码),或将红外光变换为电脉冲(译码)。IR光收发电路可以是标准IR光收发器(如TFDU4300),也可以用分立元件来实现。

MP2122器件内部由三个功能块组成(见图1):时钟驱动电路(16×CLK),复位电路以及IR标准编/译码电路。16×CLK提供电路工作所必须的时钟信号;复位电路支持外部复位信号;IR编/译码逻辑是依据IrDA标准物理层规范设计的,编码电路将8位字节数据变换为IrDA标准信号,而译码电路则将IrDA标准信号变换为8位数据字节。

MCP2122的工作需要一个外部时钟信号,16×CLK引脚就是器件时钟输入端,它与主UART接口和IR接口无关。16×CLK确定了器件工作时所有定时关系。16×CLK信号也可称为位时钟(BITCLK),每位有16个BITCKK,用来产生TXIR和IXIR的位图形。由此可知,MCP2122的波特率是由16×CLK决定的,计算公式为F16×CLK=16*(波特率)。表1示出了几种常用波特率与其相应的16×CLK频率。

IR编译码信号是这样的,如果TX引脚发送的值是个逻辑低信号,TXIR引脚则输出7个时钟周期低电平,3个时钟周期逻辑高电平,其余6个时钟周期保持低;如果发送的值是逻辑高电平,TXIR引脚在整个16位时钟周期内输出一个低电平。译码时,如果接收的值是逻辑低信号,RXIR引脚在开始3位时钟周期内是低电平,其余13位时钟周期是高电平;如果接收的值是逻辑高信号,RXIR引脚在整个16位时钟周期内是高电平。这样,RX引脚电平将处于相应的状态。

MCP2122与主控制器接口有4个信号,TX与RX连接至主控器的UART,这2个信号是有一定波特率的串行信号,由起始位、数据位和终止位组成。RESET引脚用来将MCP2122处于某个确定的状态,该引脚加以低电平时迫使其输出引脚进入默认的状态。16×CLK是器件的工作时钟,其频率应是所需波特率的16倍,为了使器件正常工作,时钟频率必须与波特率相匹配。时钟的信号源可以是:

·电路板系统时钟:这个信号是现成的,可直接连接至16×CLK引脚,唯一要注意的就是与波特率匹配问题。

·主控器I/O引脚上固件产生的时钟。主控器产生时钟信号是一件十分简单的工作,只是会占用MCU的工作时间。以PICmicroMCU为例,可以用BSF指令来产生上升边,BCF指令会产生下降边。两条指令生成一个脉冲信号,其周期(即频率)可根据波特率及指令周期来确定。

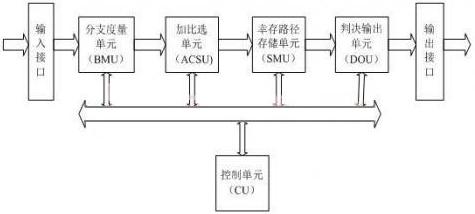

·主控器硬件产生时钟:硬件能减少固件的开销,还能使波特率更高。一个典型的PICmicro器件使用CCP模块来生成时钟。在模式初始化配置后无需额外的软件开销,且时钟与UART是同步的。CCP模是可配置成捕捉、比较或PWM工作方式的硬件模块,与主控器的TIME1或TIME2协同工作。产生16×CLK需要PWM模式,用Timer2作为时基。PIC16F877A的CCP模块处于PWM模式时的简化方框图如图2所示。PWM模式充分利用MCU内部Q时钟(一个指令周期4个Q时钟)实现50%的占空比,而最小PWM周期为指令周期。PWM周期为:

T=[(PR2)+1]×4×Tosc(TMR2预设值)

上式中,PR2为寄存器中值,Tosc为时钟振荡器周期。

评论