不同电源供电的器件间的桥接(07-100)

半导体行业从一开始就以“更小、更快、更便宜、更好”为宗旨。当前的掌上电脑(Pocket PC)比占地整整一幢楼的第一台电脑功能更强大。然而,到目前为止,实现这一目标的方法都是减小组成半导体器件的单个晶体管的体积。这也带来了有趣的副作用。随着晶体管变得越来越小,工作电压也越来越低。在过去的嵌入式系统中应用最普遍的就是5V电源。但典型嵌入式系统中的大多数元器件也转而采用更低的电源电压,以充分利用行业最新趋势带来的好处。另一方面,系统中的某些元器件需要更长的时间才能完成转变。因此,在转变过程中,系统中的某些元器件可能需要不同的供电电压(如,在3.3V系统中存在5V器件,反之亦然)。这给嵌入式设计人员带来了一些设计方面的挑战。一种解决方案是采用逻辑电平转换器,但采用电平转换器并非成本效益最高的解决方案。本文将讨论3.3V单片机(MCU)与5V外设接口的一些低成本设计思路。

如果要将5V设计转为3.3V,第一件事就是寻求电源为3.3V但其他性能相同的单片机。大多数情况下,都能找到支持3.3V电压的同等器件。而且,基本上,3.3V器件的成本与之持平,甚至更低。如果找不到可运行在3.3V条件下的替代器件,那么就必须采用双电源了。本文的重点就是讨论采用双电源供电的设计。

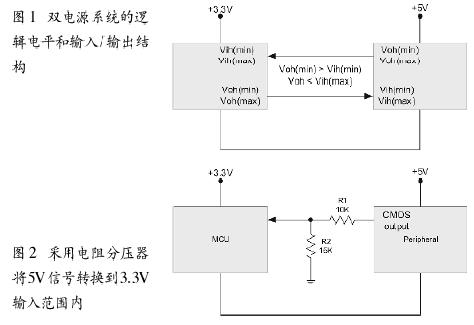

对于5V和3V器件共存的设计,首先必须理解逻辑电平和输入/输出结构。对于输入,需要考虑VIH(保证被检测为高输入的电压)和VIL(保证被检测为低输入的电压)。将3.3V系统连接到5V器件时,VIH 通常会比VIL带来更大的问题。当然,这并不是说可以忽略VIL 参数。驱动器件必须输出高于接收器件VIH(min)值的电压才能保证正确的逻辑检测。但是,如果电压太高也不好。

几乎所有CMOS器件在所有I/O引脚都采用了某种形式的ESD保护。实现ESD保护最常见的方法是采用箝位二极管将这些引脚连接到Vdd 和 Vss。这通常意味着最大输入电压为Vdd +0.3V,最小输入电压为Vss - 0.3V。如果电压超出这一范围,保护二极管就会导通。如果输入端没有串联电阻,就会导致这些二极管通过极大电流,并有可能造成器件锁死。这肯定不是所希望发生的。如果电压足够高(如3.3V系统中的5V输入),那么串联电阻必须非常大才能保证箝位电流处于安全范围内。如果电阻足够大,那么由于引脚电容和PCB布线而引起的低输入容抗可能就会变得重要起来。RC时间常数会导致信号延迟。许多生产商都建议不要使用箝位二极管实现ESD保护。因此,采用串联电阻并非将5V信号馈送到3.3V器件的最好方法。

评论