通信应用中的数字上变频和下变频(06-100)

数字上变频器(DUC)和数字下变频器(DDC)不仅仅是通信应用(如软件无线电)中的关键,而且在需要窄带信号高速流的应用中也是重要的。另外,DDC结构容易控制所有取样速率下的混淆防止分样。

本文引用地址://www.cazqn.com/article/81240.htm做为1个例子,让我们看看数字记录5MHz带宽(中心在50MHz)信号的问题。此信号可以是来自RF-IF模拟下变频器的信号或者是直接从天线接收的信号。为了满足尼奎斯特准则,我们需要以105ms/s取样率取样此信号。然而,为了合理地捕获此信号,应该在较高的取样率(至少200ms/s)取样此信号。假设ADC为16位,在该速率下被取样的信号会产生400MB/s数据。也许更难办的是以这样高速率采集和存储数据缺乏商业可用的方案。大多数可用的PC基数字器仅能在大约几分之几秒内存储此数据。

数字下变频

DDC在持续时间期间可以数字记录RF信号。在此实例中,我们仅需要记录5MHz信号(中心频率50MHz),而不是ADC的整个尼奎斯特带宽。DDC允许除去其余数据,并降低数据率。在现场可编程门阵列(FPGA)中实现时,简单的数字下变频分为3个性质不同的步:频率变换、滤波和分样(图1)。

频率变换和滤波

第1步是频率变换。5MHz频带需要降低变换到基带,靠乘或与载频(fc)正弦信号混频实现这种变换。用数字控制振荡器(NCO)数字产生正弦波。NCO通常也称之为本机振荡器(LO),它可以在精确频率和相位下产生取样波形。

随着信号从50MHz变频到基带,信号拷贝也从50 MHz变频到100 MHz。基于此原因,新的基带信号必须滤波,去除较高频率的信号。

然而,到此我们的任务没有完成。我们仍有1个在200ms/s取样的低频基带信号。传输额外不必要数据时不希望PC总线过载,我们重新取样信号来降低有效取样率。这靠分样实现,在规则的时间间隔内从数字化的信号中去除数据点。在此例中,取样从200ms/s下降到10ms/s,每20个取样去除19个取样。

防止混淆的分样

采用分样,数字化器的采集引擎继续以同样的最大速率进行取样。然而,仅有少量的采集点被存储、被取出和传输到PC,这降低取样率到所希望的水平。但是,此技术不是极简单的。

为便于说明,假定数字化器的最大取样率是100MS/s,使其尼奎斯特频率为50 MHz,而信号有两个分量:10 MHz基频和20MHz激励频率分量。若数字化器分辨率为14位,则在100MS/S总数据率是200MB/s,这远远高于PCI总线理论极限132MB/s。这是采用较低取样率(如25MS/s)的1个原因。现在尼奎斯特频率应该是12.5MHz。然而,20MHz频率分量混淆回到5MHz。现在,不可能告知信号实际上是否是5MHz信号或混淆到5MHz的另外较高频率信号(20MHz,30MHz,45MHz)。

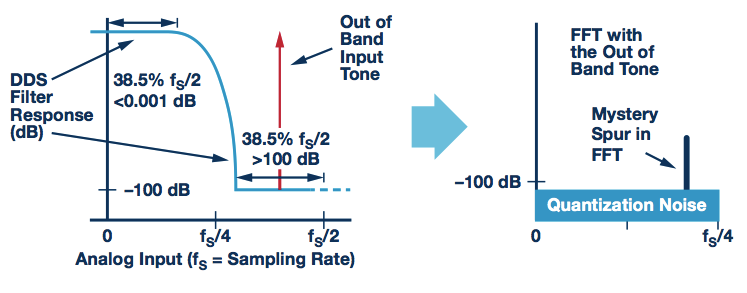

解决此问题的1种方案是称之为防止混淆分样的增强分样技术。在此技术中,数字化器继续在100MS/s最高取样率下采集数据,但加1个低通数字滤波器,在分样前截止尼奎斯特频率(图2)。

评论