存储技术,掀起一轮新革命

在 AI 应用浪潮下,高性能内存需求持续飙升,以 HBM 为代表的 DRAM 受到极大追捧。与此同时,为进一步满足市场需求,内存厂商也蓄势待发,迎来新一轮 DRAM 技术「革命」。

本文引用地址://www.cazqn.com/article/202407/461499.htm4F Square DRAM 开发顺利

三星电子副总裁刘昌植近日宣布,三星下一代 DRAM 技术进展顺利,除了成功量产 1b DRAM 外,4F Square DRAM 技术开发也进展顺利,预计 2025 年开发出 4F Square DRAM 的初始样品。

据悉,早期 DRAM 单元结构为 8F 方格,目前商用的 DRAM 主要采用 6F 方格,相比于这两种技术,4F 方格采用了垂直通道晶体管(VCT)结构,可将芯片表面积减少 30%。

由于单元面积减小,DRAM 密度与性能提升,因此在 AI 等应用的推动下,4F Square 技术逐渐受到各大存储厂商的追捧。

此前,三星表示,许多公司正在努力将其技术过渡到 4F Square VCT DRAM,尽管仍需克服一些挑战,包括开发氧化物通道材料和铁电体等新材料。

业内人士认为,三星 2025 年推出的 4F Square DRAM 首批样品或将用于内部发布。另一家半导体制造商东京电子则预计,采用 VCT 和 4F Square 技术的 DRAM 将在 2027 年至 2028 年间问世。

此外,三星计划应用 Hybrid Bonding 技术支持 4F Square DRAM 的生产。Hybrid Bonding 是下一代封装技术,指的是通过垂直堆叠芯片来增加单元密度,从而提高性能,这也将对 HBM4 和 3D DRAM 的发展产生影响。

HBM4 即将问世

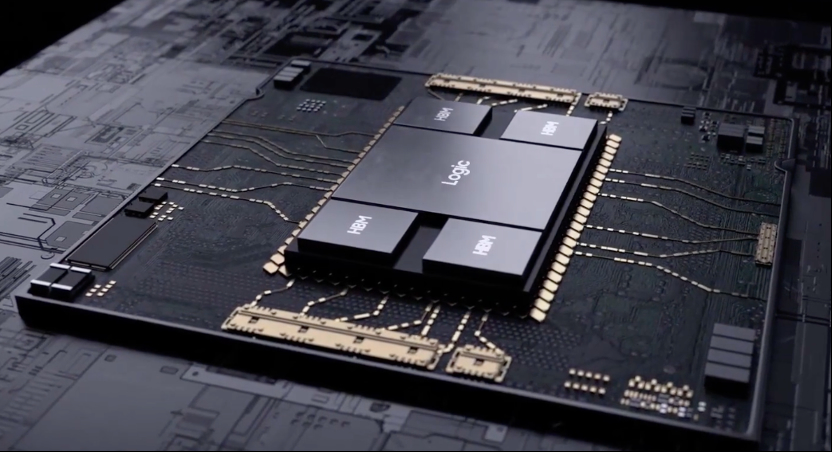

在 AI 时代,HBM 尤其是 HBM3e 在内存市场大行其道,三大 DRAM 厂商竞争愈演愈烈,而新一轮的竞争又在紧锣密鼓地进行,焦点集中在下一代 HBM4 技术上。

今年 4 月,SK 海力士宣布与台积电合作开发 HBM4。据悉,两家公司将首先针对 HBM 封装最底层的 Base Die 进行性能改进。为了专注于下一代 HBM4 技术的开发,三星专门成立了全新的「HBM 开发团队」。

7 月份,三星电子内存部门新业务规划组组长崔章锡透露,该公司正在开发一款单栈高达 48GB 的大容量 HBM4 内存,预计明年投产。据悉,三星计划采用 4nm 先进工艺生产 HBM4 逻辑芯片。而美光则计划在 2025 年至 2027 年之间推出 HBM4,并在 2028 年过渡到 HBM4E。

除了制造工艺,DRAM 制造商也在积极探索混合键合技术,以用于未来的 HBM 产品。与现有的键合工艺相比,混合键合消除了 DRAM 内存层之间凸块的需要,而是直接将上下层、铜与铜连接起来。这显著提高了信号传输速度,更好地满足了 AI 计算的高带宽要求。

今年 4 月,三星成功基于混合键合技术制造出 16 层堆叠 HBM3 存储器,存储器样品运行正常。未来,该 16 层堆叠混合键合技术将用于规模生产 HBM4。SK 海力士计划在 2026 年之前将混合键合应用于 HBM 生产。美光也在开发 HBM4,并考虑包括混合键合在内的相关技术,目前这些技术都在研究中。

3D DRAM 发展势头强劲

3D DRAM(三维动态随机存取存储器)是一种具有新颖存储单元结构的新型 DRAM 技术。与水平放置存储单元的传统 DRAM 不同,3D DRAM 垂直堆叠存储单元,大大增加了单位面积的存储容量并提高了效率。这使其成为下一代 DRAM 的关键发展方向。

在存储器市场,3D NAND Flash 已实现商业化应用,3D DRAM 技术尚在研发中,但随着 AI、大数据等应用的蓬勃发展,大容量、高性能存储器需求将大幅增加,3D DRAM 有望成为存储器市场的主流产品。

HBM 技术为 DRAM 的 3D 演进铺平了道路,使 DRAM 从传统的 2D 过渡到 3D。不过,目前的 HBM 还不能算是真正的 3D DRAM 技术。三星的 4F Square VCT DRAM 更接近 3D DRAM 的概念,但并不是 3D DRAM 的唯一方向或目标。内存厂商在 3D DRAM 方面还有更多的想法和创意。

三星计划在 2030 年实现 3D DRAM 的商业化,2024 年三星展示了两种 3D DRAM 技术,包括 VCT 和堆叠 DRAM。三星先是推出了 VCT 技术,随后通过将多个 VCT 堆叠在一起升级为堆叠 DRAM,不断提升 DRAM 的容量和性能。

三星表示,堆叠式 DRAM 可充分利用 Z 轴空间,在更小的面积内容纳更多存储单元,单芯片容量可超过 100Gb。今年 5 月,三星指出,已与其他公司一起成功制造出 16 层 3D DRAM,但强调尚未做好量产准备。3D DRAM 预计将采用晶圆到晶圆混合键合技术生产,同时也考虑采用 BSPDN(背面电源传输网络)技术。

美光已提交了与三星不同的 3D DRAM 专利申请,旨在改变晶体管和电容器的形状,而无需放置单元。

SK 海力士的 5 层堆叠 3D DRAM 的制造良率达到 56.1%。这意味着在一块测试晶圆上生产的约 1000 个 3D DRAM 中,约有 561 个可行器件被制造出来。实验性的 3D DRAM 表现出与目前使用的 2D DRAM 类似的特性,这是 SK 海力士首次披露其 3D DRAM 开发的具体数字和特性。

此外,美国公司 NEO Semiconductor 也在致力于 3D DRAM 的研发,去年 NEO Semiconductor 宣布推出全球首款 3D DRAM 原型产品:3D X-DRAM,该技术类似 3D NAND Flash,即通过堆叠层数来增加内存容量,具有高良率、低成本、高密度等特点。

NEO 半导体计划在 2025 年推出第一代 3D X-DRAM,其堆栈为 230 层,核心容量为 128Gb,比 2D DRAM 的 16Gb 容量高出数倍。

评论