台积电要抄三星的后路

在芯片制造领域,先进制程的影响力和统治力越来越大,已经从之前的逻辑芯片晶圆代工领域,拓展到最先进的存储芯片制造,这在台积电和三星身上有凸出的体现。

本文引用地址://www.cazqn.com/article/202407/461288.htm当下的 3nm 制程晶圆代工,台积电的市场统治力很明显,三星处于弱势地位。未来的 2nm 制程,三星必须加紧赶上,否则会越来越困难。

在高带宽内存(HBM)芯片制造方面,原本都由存储芯片 IDM 大厂自家完成,但是,到了下一代的 HBM4,技术难度和制造难度提高了不少,需要更先进的制程工艺参与进来。

2nm 制程针锋相对

据报道,台积电将于 7 月中旬开始试生产 2nm 制程工艺芯片,早于市场预估的第四季度。

台积电 2nm 工艺首次应用 GAA(全环绕栅极晶体管)技术,可以在更小的制程节点上提供更好的性能。

据台积电介绍,与 3nm 制程相比,2nm 的能效提升 10%~15%,功耗降低 30%。当试产良率达到一定标准时,便可以推进到量产阶段。

台积电的 2nm 制程将包括 N2、N2P 和 N2X 三个版本,预计 2025 下半年开始量产其第一代 GAAFET N2 节点芯片,下一个版本 N2P 将在 2026 年底量产。台积电这两个版本 2nm 工艺没有使用背面供电技术,不过,整个 N2 系列将增加台积电新的 NanoFlex 功能,该功能允许芯片设计人员在同一模块中匹配来自不同库(高性能、低功耗、不同面积)的单元,以提高性能或降低功耗。

N2P 之后将是电压增强型的 N2X。尽管台积电曾表示 N2P 将在 2026 年增加背面供电技术,但看起来情况并非如此,N2P 将使用常规供电电路,具体原因尚不清楚。

有消息称苹果已经与台积电达成独家协议,包下台积电 2nm 制程首批全部产能。

据外媒报告,台积电 2024 年资本支出可能达到上限值 320 亿美元,2025 年有望进一步升至 370 亿美元,主要用于提前部署 2nm 工艺量产,采购先进设备。目前,三星也在发力 2nm 工艺,台积电提前部署产能的目的是为保持在晶圆代工领域的领导地位。

今年初就有报道称,三星已经从日本人工智能(AI)初创公司 Preferred Networks Inc.(PFN)收到 2nm 制程芯片订单,从而在 2nm 晶圆代工业务中抢得先机。

7 月 9 日,三星发布公告,官宣了与 Preferred Networks Inc. 的合作,将基于 2nm 制程工艺和 2.5D 封装技术 Interposer-Cube S(I-Cube S),提供一站式解决方案,为对方制造 AI 芯片。

Preferred Networks Inc. 主要进行人工智能深度学习开发。据悉,三星之所以被选中,是因为其同时具备存储器和晶圆代工服务,有着较强的综合能力和技术积累,可以提供 HBM 设计、生产和先进封装的全套解决方案。

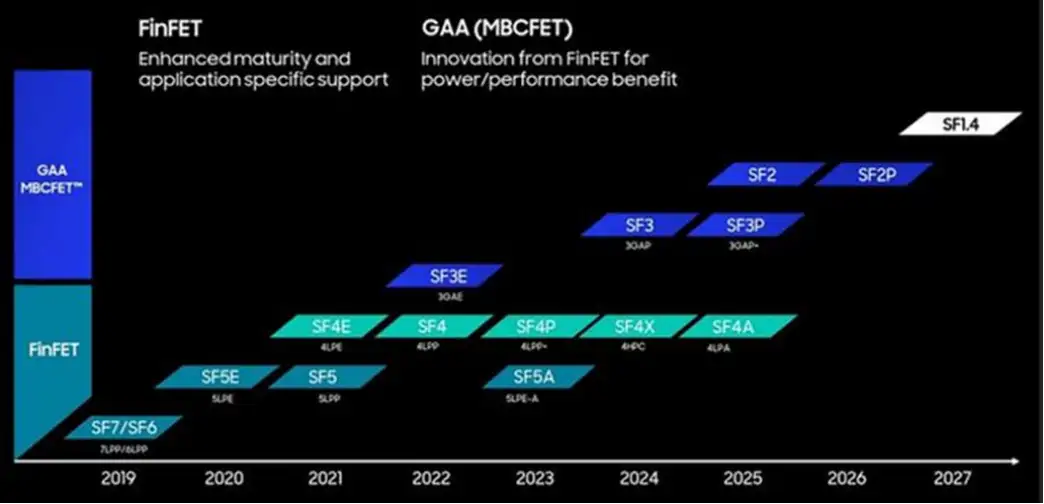

三星原计划 2025 年量产 2nm(SF2)制程芯片,然后于 2026 年采用背面供电技术。与 3nm 工艺(SF3)相比,三星的 2nm 工艺性能提升 12%,功率效率提升 25%,面积减少 5%。

台积电和三星在 2nm 制程芯片量产方面在较劲,双方也都有需要解决的问题。

IBS 估计,与 3nm 处理器相比,2nm 芯片成本将增长约 50%。

正是有苹果、英伟达、AMD 等大客户下单,台积电才会大规模投资最先进制程,否则,像 2nm 这样烧钱的制程产线,是很难持续支撑下去的。目前,台积电正在全方位控制成本,包括 EUV 设备的支出,电能的节省等。虽然其它几家厂商也会面临 2nm 成本问题,但为了追赶台积电,三星和英特尔似乎在成本方面没有台积电那么敏感。另外,由于台积电要在美国新建至少两座先进制程晶圆厂,这给它带来了很多额外的成本压力。因此,台积电的 2nm 制程产线必须精打细算。

对于晶圆代工来说,良率非常重要,它直接影响生产成本和客户认可度。

自从进入 5nm 制程时代以来,良率一直是三星晶圆代工业务所面对的最大问题,特别是在 3nm 制程节点上,三星率先引入了全新的 GAA 架构晶体管,与以往使用的 FinFET 晶体管有较大区别,制造难度增加不少。

据 Notebookcheck 报道,三星的 3nm 工艺良率在 50% 附近徘徊,依然有一些问题需要解决。

今年 2 月,据韩媒报道,三星新版 3nm 工艺存在重大问题,试产芯片均存在缺陷,良率为 0%。报道指出,采用 3nm 工艺的 Exynos 2500 芯片因缺陷未能通过质量测试。

为了追赶台积电,三星的 3nm 制程工艺采取了比较激进的策略,主要体现在 GAA 晶体管架构上,台积电的 3nm 依然采用 FinFET。2nm 才会转向 GAA 晶体管,激进的结果就是要在良率方面付出一些代价。

台积电统治 3nm 代工

据了解,台积电 3nm 制程产能已经被各大客户预定到 2026 年。

最新一波订单正在被联发科和高通争抢。新一轮 5G 手机旗舰芯片大战将于今年第四季度开打,联发科的天玑 9400 和高通的骁龙 8 Gen 4 对决,两大厂商的新处理器都将采用台积电 3nm 制程生产,近期进入投片阶段,使得相关产能更加紧张,因为英伟达、AMD、苹果都在积极争取更多台积电 3nm 产能。据悉,台积电计划将今年的 3nm 制程产能扩充 3 倍,但仍呈现供不应求的局面。

为了让天玑 9400 顺利上市,联发科正在努力确保 3nm 制程产能供应。目前,联发科的旗舰款天玑 9300/9300+芯片,都是用台积电 4nm 制程制造。

高通虽尚未公布新一代旗舰芯片骁龙 8 Gen 4 亮相时间和细节,外界认为,该款芯片也将采用台积电 3nm 制程生产,并于第四季度推出,芯片性能也将升级。据悉,骁龙 8 Gen 4 将采用台积电 N3E 制程生产,每个芯片报价 220~240 美元,比骁龙 8 Gen 3 高出 25%~30%。

据悉,台积电打算提高 2025 年先进制程工艺和先进封装的订单报价,其中,3nm 的报价将提高 5% 以上,具体情况取决于订单的数量和协议条款,目前的晶圆报价在 20000 美元以上。CoWoS 封装的报价将提高 10%~20%。传闻台积电的 3nm 涨价方案已得到客户的同意,双方达成了新协议,以确保稳定的供应。

此外,有业内人士透露,面向高性能计算客户的 4nm/5nm 制程工艺可能会涨价 11%,也就是说 4nm 晶圆的价格从 18000 美元提高到约 20000 美元,比 2021 年的报价上涨了至少 25%。

台积电的 3nm、4nm、5nm 制程都要涨价,从一个侧面说明三星在这些制程市场上的窘境,因为全球只有这两家能够提供相应制程工艺的量产代工产能,为了追赶台积电,自从 7nm 制程实现量产以来,很多年,三星都是在低价促销,特别是最先进的 3nm 制程工艺,比台积电的报价少了很多。如今,竞争对手的产能供不应求,还要涨价,说明三星 3nm 的客户订单少得可怜,台积电才有底气涨价。

总之,在已经量产的最先进制程方面,台积电优势明显,三星在这方面的竞争力已经很难追赶上,只能寄希望于 2nm 制程了。

台积电要在 HBM 市场分一杯羹

7 月初,据韩国媒体报道,SK 海力士将深化与台积电、英伟达的合作,并在 9 月的国际半导体展(Semicon Taiwan)上,宣布这三家公司更紧密的合作计划。

2022 年,台积电在北美技术论坛宣布成立 OIP 3DFabric 联盟,将存储器与载板合作伙伴纳入,当时,SK 海力士资深副总裁暨 PKG 开发主管 Kangwook Lee 就透露,该公司一直和台积电在前几代及目前的 HBM 技术方面紧密合作,以支持 CoWoS 制程的兼容性与 HBM 的互连性。SK 海力士加入 3DFabric 联盟之后,通过与台积电更深入的合作,为未来的 HBM 产品(HBM4)提供解决方案.

据韩国媒体报道,业界消息人士称,SK 海力士社长金柱善将于 9 月在台北举行的国际半导体展上发表专题演讲,这是 SK 海力士首度参与专题演讲。演讲结束后,金柱善将和台积电高级主管见面,讨论下一代 HBM 的合作计划,英伟达 CEO 黄仁勋也可能加入会谈,进一步巩固 SK 海力士、台积电和英伟达之间的三方联盟。

据悉,三强的合作是在 2024 上半年敲定的,SK 集团会长崔泰源 4 月会见黄仁勋,讨论了半导体合作事宜,6 月,崔泰源拜访了台积电新任董事长魏哲家,以进一步推动后续合作。

SK 海力士将采用台积电的逻辑制程,生产 HBM 的基础接口芯片(base die)。报道称,SK 海力士和台积电已同意合作开发并生产 HBM4,将于 2026 年量产。

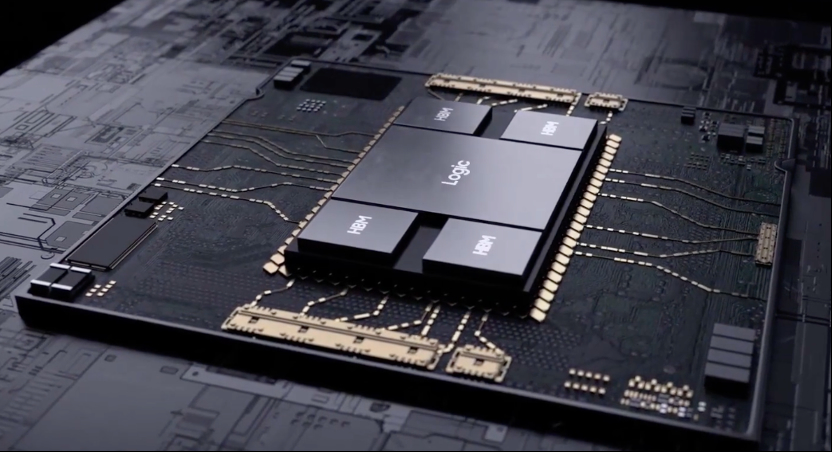

HBM 将核心芯片堆叠在基础接口芯片之上,彼此垂直相接。SK 海力士生产的 HBM3E 产品,采用的是自家制程工艺制造的基础接口芯片,但从 HBM4 开始,将采用台积电的先进逻辑制程。报道称,SK 海力士将在论坛上介绍合作成果,据悉,HBM4 的功耗比原本目标还低 20% 以上。

自从 HBM 问世并量产以来,SK 海力士一直是英伟达为其 AI GPU 配备该类内存的独家供应商,发展到 HBM3E 版本,依然如此,只是从 2024 年第二季度开始,另外两家内存大厂三星和美光才开始加入英伟达 HBM 供应链,这两家内存大厂准备花费数十亿美元来扩大 HBM 芯片生产能力。

不久前,三星推出了其 12 层堆叠的 HBM3E,挑战 SK 海力士 8 层堆叠产品的行业地位。三星的一位高管表示,该公司计划今年将芯片产量增加两倍。面对竞争,SK 海力士的 HBM 项目正在提速,预计首批 12 层堆叠的下一个版本 HBM4 最快会在 2025 下半年到来,到 2026 年还会有 16 层堆叠的产品,会向更加定制化的方向发展。

HBM3E 市场竞争已经落后,希望落在了 HBM4 上,三星正在加快研发脚步,以缩小与 SK 海力士之间的差距。在代号为「Snowbolt」的第六代 HBM 芯片 HBM4 方面,三星计划将缓冲芯片应用于堆叠内存的底层以提高效率。

正当三星加紧追赶存储芯片竞争对手 SK 海力士的时候,后者与三星的晶圆代工「死敌」台积电在深化合作。对三星来说,这显然是个坏消息。

5 月中旬,在 2024 年欧洲技术研讨会上,台积电表示,将使用其 12FFC+(12nm 级)和 N5(5nm 级)制程工艺制造 HBM4 接口芯片。

台积电设计与技术平台高级总监表示:「我们正在与主要的 HBM 内存合作伙伴合作,开发 HBM4 全栈集成的先进制程,N5 制程可以使 HBM4 以更低的功耗提供更多的逻辑功能。」据悉,N5 制程允许将更多的逻辑功能封装到 HBM4 中,并实现非常精细的互连间距,这对于逻辑芯片上的直接键合至关重要,可以提高 AI 和 HPC 处理器的内存性能。

相对于 N5,台积电的 12FFC+工艺更加经济,制造的基础芯片能构建 12 层和 16 层的 HBM4 堆栈,分别提供 48GB 和 64GB 的容量。

台积电还在优化封装技术,特别是 CoWoS-L 和 CoWoS-R,以支持 HBM4 集成。这些先进的封装技术有助于组装 12 层的 HBM4 内存堆栈。据台积电介绍,实验性 HBM4 内存在 14mA 时的数据传输速率已达到 6 GT/s。

台积电的先进制程工艺能力,以及 SK 海力士的先进存储芯片制造能力,可以将结构更为复杂的 HBM4 内存的制造分解开,发挥各自优势,制造出最佳的逻辑接口和 DRAM 裸片,然后用先进的封装技术将它们组装起来,以最大化地发挥该类内存的性能优势。

对三星来说,在先进制程晶圆代工市场被台积电压制,但作为存储芯片龙头企业,三星还是很自信的。如今,台积电与自己的主要竞争对手 SK 海力士在内存领域深度合作,简直是在抄三星的后路。要发展 HBM4,就绕不开先进的逻辑芯片制程工艺,如果三星的晶圆代工业务短期内做不好这些的话,恐怕也躲不开找台积电合作的选项。

评论