台积电CEO秘访ASML,High-NA EUV光刻机竞赛提前打响?

5月26日,台积电举办“2024年技术论坛台北站”的活动,台积电CEO魏哲家罕见的没有出席,原因是其秘密前往荷兰访问位于埃因霍温的ASML总部,以及位于德国迪琴根的工业激光专业公司TRUMPF。

本文引用地址://www.cazqn.com/article/202405/459384.htmASML CEO Christophe Fouquet和其激光光源设备供应商TRUMPF CEO Nicola Leibinger-Kammüller近日通过社交媒体透露了魏哲家秘密出访的行踪。Christophe Fouquet表示他们向魏哲家介绍了最新的技术和新产品,包括High-NA EUV设备将如何实现未来的半导体微处理技术。

此前报道,台积电计划2026年下半年量产1.6nm制程工艺(A16)之后引入High-NA EUV光刻机。魏哲家对ASML总部的秘密访问让人颇感意外,可能与台积电目前正在考虑如何实现更先进的工艺技术有关。

台积电业务开发资深副总经理张晓强于5月14日出席在阿姆斯特丹举办的技术研讨会上表示:“ASML的High-NA EUV太贵了,我非常喜欢High-NA EU的能力,但不喜欢它的价格”。High-NA EUV光刻机的价格约为3.5亿欧元,相比之下,现有的EUV光刻机价格约为1.7亿欧元。

根据台积电的既定计划,A16工艺节点不需要使用High-NA EUV光刻机,现有的旧款EUV设备能够完成。虽然台积电公开表示A16将不会采用High-NA EUV光刻机,但是本次的密访动作似乎显示对这一明确的立场有了新的想法,有可能会修正其既定计划,提前导入High-NA EUV光刻机进行试验和学习。台积电何时使用ASML的最新技术将取决于何时最具成本效益,以及技术成熟度的平衡点。

为什么需要High-NA光刻机?

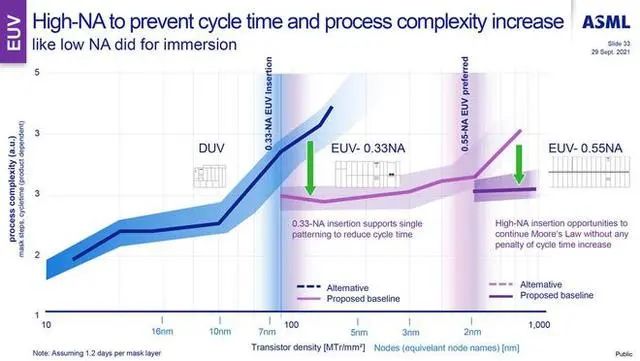

从早期的深紫外光刻机(DUV)起步,到后来的极紫外光刻机(EUV)以其独特的极紫外光源和更短的波长,再到如今的高数值孔径光刻机(High-NA)正式登上舞台,为制造更小、更精密的芯片提供了可能。

光刻分辨率(R)主要由三个因数决定,分别是光的波长(λ)、光可穿过透镜的最大角度(镜头孔径角半角θ)的正弦值(sinθ)、折射率(n)以及系数k1有关。而为了减小可光刻的最小特征的尺寸(称为临界尺寸 , CD),可以通过调整两个主要的参数:光的波长λ和数值孔径NA。

进入EUV世代则对波长参数进行重大调整 —— 使用13.5nm光,而最高分辨率DUV系统则使用193nm光。改变波长之后再进一步提升EUV光刻机的分辨率就要从NA指标上下手了,“NA”即光学系统的数值孔径,表示光线的入射角度,使用更大的NA透镜可以打印出更小的结构。

目前ASML已经开始交付的首款High-NA EUV系统数值孔径已经由传统EUV的0.33提升到了0.55,分辨率也由13.5nm提升到了8nm,可以实现16nm的最小金属间距,对于2nm以下制程节点将非常有用。另外,在生产效率方面,High-NA EUV系统每小时可光刻超过185个晶圆,与已在大批量制造中使用的EUV系统相比还有所增加。ASML还制定了到2025年将新一代High-NA EUV系统(EXE:5200)的生产效率提高到每小时220片晶圆的路线图。

英特尔希望在2nm领域拔得头筹

为了在先进制程技术上重回领先地位,英特尔已经率先斥巨资拿下了ASML的首批High-NA EUV光刻机,预计先在即量产的Intel 18A制程节点上进行验证和学习,然后再将High-NA EUV光刻机应用于Intel 14A制程的量产。

上个月英特尔晶圆代工(Intel Foundry)宣布,已在美国俄勒冈州希尔斯伯勒的英特尔半导体技术研发基地完成了业界首台High-NA EUV光刻机组装工作。随后开始在Fab D1X进行校准步骤,为未来工艺路线图的生产做好准备。

2011年英特尔首发了FinFET工艺,22nm FinFET工艺当时远超台积电、三星的28nm,技术优势可谓是遥遥领先,然而在14nm节点之后,英特尔接连遭受了重创,无法跟上台积电推出10nm、7nm和5nm工艺的节奏。从14nm到10nm的艰难量产,让英特尔在2021年提出IDM2.0战略,打破“自家芯片自家造”的传统,将芯片生产独立运营出来:对外开放自己的代工服务,同时扩大采用第三方代工产能。

目前,英特尔代工(由制造部门组成)和英特尔产品(由产品业务部门组成)之间建立了代工关系。这不仅是一次简单的结构重组,更是对未来战略方向的明确宣示,体现了英特尔向代工运营模式即Intel Foundry的转变,实现到2030年成为全球第二大代工厂的目标。目前英特尔正在不断加强代工基础设施建设,计划未来5年投资1000亿美元扩大先进芯片制造能力。

值得注意的是,尽管英特尔雄心勃勃,但由于四年五个节点及路线演进、生态构建和产能扩建等巨额的投入,其代工业务去年营收同比下降31.2%至189亿美元,经营亏损70亿美元,同比扩大34.6%。对英特尔来说,芯片制造能力是独有的优势,但也意味着高投入和沉重的负担,晶圆厂建置成本极高。根据机构估算,建造一座月产量在5万片晶圆的2nm工厂需要的成本约为280亿美元,而同样产能的3nm工厂的成本约为200亿美元。

2024年有可能将是英特尔芯片制造业务经营亏损最严重的一年,从今年一季度财报来看,该业务运营亏损25亿美元,几乎是上一季度的两倍。“四年五个制程节点”计划的启动成本达到顶峰,而且大部分产量都在EUV之前的工艺节点上,经济性缺乏竞争力。然而随着完成“四年五个制程节点”计划,实现制程工艺重回领先地位,通过产量组合转向领先的EUV节点,运营利润率预计将得到提升。

台积电选择平衡成本和技术

按照半导体行业的摩尔定律,集成电路可容纳的晶体管数目,每隔18个月便会增加一倍,性能相应也增加一倍。台积电董事长刘德音最近在IEEE网站上署名发表文章,把半导体行业过去50年缩小芯片尺寸的努力比作“在隧道中行走”。如今距离摩尔定律的极限越来越近,行业已经走到隧道的尽头,半导体技术将变得更加难以发展,2nm将会是芯片巨头抢滩的关键一战。

相比于激进的英特尔,台积电却依旧“淡定”,公开表示其现拥有的低噪点EUV光刻机阵容可以支持生产到2026年。在前不久台积电举办的2024年北美技术论坛,台积电首次公布了A16制程工艺,并透露A16制程工艺不需要采用下一代High-NA EUV光刻机。

台积电让现有EUV发挥“余热”,通过提高生产效率的多重掩模和先进的基于纳米片的晶体管设计,找到了实现1.6nm的途径。尽管相对工艺步骤多、周期长、成本高,但采用高NA光刻机可能风险更大,台积电应是认为采用原有的EUV更为经济且可行,在成本和技术之间寻求了平衡。

台积电于2019年开始在其N7+工艺上使用EUV,通过优化EUV曝光剂量及其使用的光刻胶,改进光罩薄片延长寿命、提升产量、降低缺陷率等等,如今光刻机数量增加了十倍,但晶圆产出是2019年的30倍,且仍将持续改进,这也成为其未来支撑1.6nm工艺的重要支柱。

台积电A16工艺将结合GAAFET与背面供电,以提升逻辑密度和能效。与N2P相比,A16工艺芯片预计在相同电压和复杂度下性能提升8%-10%,在相同频率和晶体管数量下功耗降低15%-20%,且密度将提升1.1倍。

在之前的2nm节点,台积电已全面导入GAAFET晶体管技术,因而其1.6nm工艺更突出的特征还在于背面供电。作为继工艺缩进、3D封装后第三个提高芯片晶体管密度和能效的革新之一,背面供电不仅是半导体工艺创新的重要发展方向之一,也成为先进工艺比拼的新“竞技场”。

有分析称,台积电的背面供电尽管比英特尔推出晚了一两年,但其新型超级电源轨BSPDN技术将背面电源网络直接连接到每个晶体管的源极和漏极,比英特尔PowerVia与晶体管开发分开的方案更为复杂,在面积缩放层面更为有效。

此前ASML首次财务官Roger Dassen在接受采访时表示,High-NA EUV光刻机可以避免制造上双重或四重曝光带来的复杂性,在逻辑和存储芯片方面是最具成本效益的解决方案,对于提高制程效率和性能方面具有巨大潜力。由于计划会根据现有技术的表现以及其他市场因素而改变,所以台积电最后也可能会改变引入High-NA EUV光刻技术的时间点。

但是引入High-NA EUV光刻机也需要解决相应的挑战,如可以支持光子散粒噪声和生产力要求的光源、满足0.55NA小焦点深度的解决方案、计算光刻能力、掩膜制造和计算基础设施包括新型材料等等,加上一定的调试和开发时间,兼顾稳定性,投入的时间和隐形的成本可以想见。

用户最关心的是总成本问题,芯片制造商可能更愿意使用更经济可行的Low-NA EUV以双重曝光或采用先进封装技术作为补充。此外,市场需求也需考量。采用High-NA EUV光刻机制造的芯片成本巨增,虽然每片晶圆切割的芯片更多,但需要销售更多的芯片才能弥补投入,单靠手机AP芯片市场难以支撑,AI芯片的需求能否有足够的量来消化成本仍待观察。

细究台积电的成功之路,台积电从来就不争“第一个吃螃蟹者” —— 当三星在2018年开始在其7nm工艺中使用EUV之际,台积电依靠成熟的DUV光刻机仍成功地开辟了首条7nm产线,巧妙地避开了当时EUV光刻机的不完善和高昂成本,直到EUV的稳定性和成熟性得到确认,相较之下,虽然三星率先采用EUV但由于良率问题反而让台积电后来居上;对于GAAFET台积电也并没有急于使用,而是依旧选择稳妥的FinFET路线,尽管三星在3nm先声夺人但良率过低和反复跳票又让台积电在3nm后发先至。

这些都印证了台积电在技术进阶路线选择上的准确判断,接下来的问题是此前台积电在1.6nm工艺划的High-NA EUV光刻机“红线”,未来具体在哪一节点引入成为业界关注的话题。

目前ASML每年High-NA EUV光刻机的产能大概在5到6台,今年生产的这些设备将全部运往美国的芯片制造商,而英特尔已经获得了明年上半年之前生产的大部分High-NA EUV光刻机,这很大程度上得益于新设备出现时,英特尔选择了抢先下单。三星和SK海力士则预计在明年下半年也将取得High-NA EUV光刻机。

不过,EUV光刻技术或非是通向先进制程的必由之路。未来几年可能会出现所谓下一代光刻技术,如NIL(纳米压印光刻),EUV光刻机在制造晶体管时会遇到它的物理极限。NIL光刻机最大的好处是光源相对便宜,即不需要用能源转换效率低的EUV的激光源,而是只用一些DUV或者是更成熟的光源就可以结合纳米涂层的方法实现2nm/1nm制程的量产。

评论