AI芯片供不应求:英伟达、AMD包下台积电两年先进封装产能

据《台湾经济日报》报道,英伟达、AMD两家公司重视高性能计算(HPC)市场,包下台积电今明两年CoWoS与SoIC先进封装产能。台积电高度看好AI相关应用带来的动能,台积电对AI相关应用的发展前景充满信心,该公司总裁魏哲家在4月份的财报会议上调整了AI订单的预期和营收占比,订单预期从原先的2027年拉长到2028年。

本文引用地址://www.cazqn.com/article/202405/458411.htm台积电认为,服务器AI处理器今年贡献营收将增长超过一倍,占公司2024年总营收十位数低段百分比,预计未来五年服务器AI处理器年复合增长率达50%,2028年将占台积电营收超过20%。

全球云服务公司(如亚马逊 AWS、微软、谷歌、Meta)正在积极投入AI服务器军备竞赛。英伟达、AMD的产品供不应求,他们全力向台积电下单,以应对云服务公司的大量订单需求。

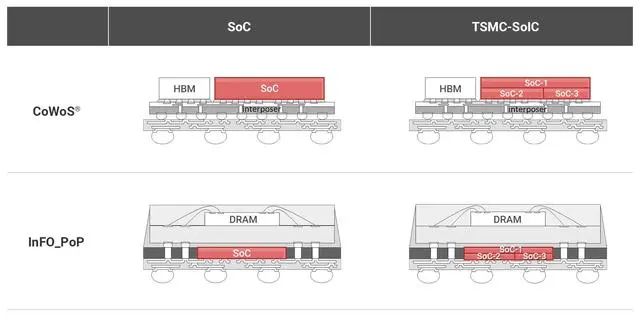

英伟达目前的主力产品H100芯片主要采用台积电4nm制程,并采用CoWoS先进封装,与SK海力士的高带宽内存(HBM)以2.5D封装形式提供给客户;AMD的MI300系列则采用台积电5nm和6nm制程生产,与英伟达不同的是,AMD先采用台积电的SoIC将CPU、GPU芯片做垂直堆叠整合,再与HBM做CoWoS先进封装。

台积电当前凭借其领先业界的2.5D/3D先进封装吃下市场几乎所有5nm及以下制程高端芯片封装订单,并且先进封装产能远无法满足需求,英伟达H100/H200供不应求正是受限于台积电2.5D级别的CoWoS封装产能。为应对客户的巨大需求,台积电正在积极扩充先进封装产能。今年底台积电的CoWoS月产能将达到4.5万至5万片,SoIC预计今年底月产能可达五、六千片,并在2025年底冲上单月1万片规模。

CoWoS

CoWoS(Chip On Wafer On Substrate)是一种2.5D的整合生产技术,由CoW和oS组合而来:先将芯片通过Chip on Wafer(CoW)的封装制程连接至硅晶圆,再把CoW芯片与基板(Substrate)连接,整合成 CoWoS。

SoIC

SoIC于2018年4月公开,是台积电基于CoWoS与多晶圆堆叠(WoW)封装技术,开发的新一代创新封装技术,这标志着台积电已具备直接为客户生产3D IC的能力。

相较2.5D封装方案,SoIC的凸块密度更高,传输速度更快,功耗更低。

随着在硅片上压缩更多晶体管的成本越来越高,chiplet先进封装是一个吸引全球芯片公司关注的领域。在我们所处的“后摩尔时代”(Post-Moore Era),芯片先进制程突破面临极大难度(如量子隧穿效应以及开发成本指数级增长),加之逐渐迈入AI时代以及万物互联趋势愈发明显,多种任务带来的算力需求可能激增,比如深度学习任务、训练/推理、AI驱动的图像渲染、识别等。这些任务对硬件性能要求都非常高,这意味着像PC那样单独集成的CPU或GPU已经无法满足算力需求。

因此,Chiplet先进封装应运而生。Chiplet封装技术可以使不同的GPU模块,或者CPU、FPGA、ASIC芯片等在同一个系统中协同工作,最大化地高效调度各类型芯片算力,以提供更大规模的并行计算能力。IDC预计至2024下半年,台积电CoWoS产能有望大幅增加约130% 。

当前AI芯片需求可谓无比强劲,未来很长一段时间可能也是如此,而AI芯片制程主要集中于5nm以及以下的先进制程。根据市场研究机构Gartner最新预测,到2024年AI芯片市场规模将较上一年增长 25.6%,达到671亿美元,预计到2027年,AI芯片市场规模预计将是2023年规模的两倍以上,达到1194亿美元。知名市场研究机构Precedence Research近期发布的AI芯片市场规模预测报告显示,预计到2032年涵盖CPU、GPU、ASIC以及FPGA等类型AI芯片市场规模将从2023年的约219亿美元激增至2274.8亿美元,2023-2032年复合增速接近30%。

评论