AI如何赋能半导体产业发展?

1956 年是公认的人工智能元年。这一年,在美国汉诺斯小镇宁静的达特茅斯学院中,举行了一场影响深远的研讨会。在这次研讨会上,参会成员讨论了多项在当时的计算机技术水平都还没有解决的问题。在这次头脑风暴式的会议中,「人工智能」的概念第一次被提出,人工智能正式被看作一个独立的研究领域。

本文引用地址://www.cazqn.com/article/202404/457865.htm但受限于当时的计算机算力的限制,人工智能(Artificial Intelligence,简称 AI)始终没有走到前台应用。随着摩尔定律的发展,芯片的集成度越来越高,计算能力也得到了空前的发展。纵观人工智能的发展历程,一个显著的特征就是算力与算法的共同进步。得益于半导体制造技术的发展,AI 的实现成为了可能。

随着近年来 Chatgpt 的大热,AI 迅速火出圈,引起了业界的极大关注,也激发了半导体产业对人工智能芯片的市场需求,全球迎来了一波以人工智能为引领的科技浪潮,也由此,人工智能被戏称为「第四次科技革命」。

实际上,除了当下火热的 Chatgpt 等被应用于文本和图像生产外,AI 也正在赋能各行各业,比如半导体制造领域也逐渐引入了 AI 技术。

EDA 工具与人工智能

Cadence 副总裁、中国区总经理汪晓煜认为,「摩尔定律推动工艺提升,线宽缩小势必带来更复杂和更大规模的设计。尽管考虑经济效益,可以采用 3DIC 和先进封装设计,但对散热、信号完整性、电磁效应、良率和可靠性都产生一系列的挑战,基于传统 EDA 设计流程已然难以应对挑战。」

汪晓煜指出,EDA 工具需更快响应新需求,需要更进一步的智能化,实现多运算、多引擎才能加快芯片迭代速度,支撑半导体业向后摩尔时代发展。利用 LLM 技术将生成式 AI 扩展到设计流程中,可以有效提升验证和调试效率,加速从 IP 到子系统再到 SoC level 的代码迭代收敛。

Cadence 因此推出了 JedAI 平台。通过 JedAI 平台,设计流程可从大量数据中通过自主学习,不断优化,进而最终减少设计人员的人工决策时间,大幅提升生产力,从而不断地提升生产力。

通过 JedAI 平台,Cadence 将统一旗下各种 AI 平台的大数据分析——包括 Verisium 验证、Cerebrus 实现和 Optimality 系统优化,及其他第三方硅生命周期管理系统。利用 JedAI 平台,用户可以轻松管理设计复杂性越来越高的新兴消费、超大规模计算、5G 通信、汽车电子和移动等相关应用。客户在使用 Cadence 模拟/数字/PCB 实现、验证和分析软件(甚至第三方应用)时,都可以通过 JedAI 平台来统一部署其所有的大数据分析任务。

此外,Cadence 的布局布线工具 Innovus,里面也内置了 AI 算法,以提升 Floorplan 的效率和质量。Project Virtus,通过机器学习解决 EM-IR 和 Timing 之间的相互影响;还有 Signoff Timing 和 SmartLEC 等工具,都嵌入了人工智能算法。

除 Cadence 外,Synopsys 也在 2020 年推出了业界首个用于芯片设计的自主人工智能应用程序——DSO.ai (Design Space Optimization AI)。作为一款人工智能和推理引擎,DSO.ai 能够在芯片设计的巨大求解空间里搜索优化目标。该解决方案大规模扩展了对芯片设计流程选项的探索,能够自主执行次要决策,帮助芯片设计团队以专家级水平进行操作,并大幅提高整体生产力,从而在芯片设计领域掀起新一轮革命。

将 AI 技术与 EDA 工具结合,有两个核心价值,首先是力图让 EDA 更加智能,减少重复且繁杂的工作,让使用者用相同甚至更短时间设计出 PPA 更好的芯片;其次是大幅降低使用者的门槛,解决人才短缺的挑战。

OPC 与人工智能

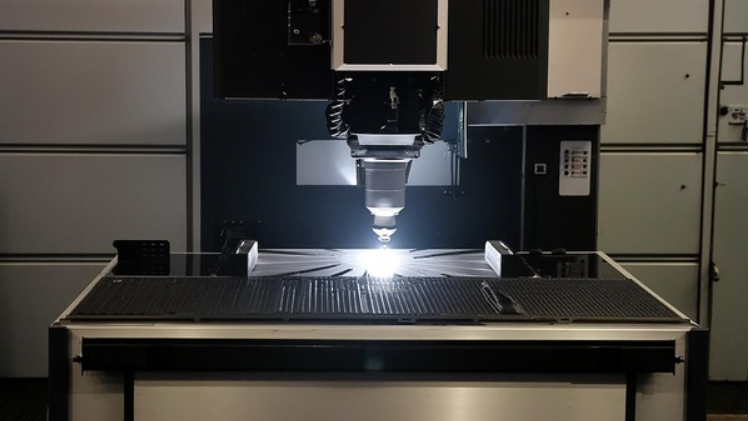

除了在设计环节的 EDA 中大量使用了 AI 技术外,芯片制造环节也逐渐引入了人工智能技术。在半导体制造业中,人工智能尤其是机器学习有全面的应用场景,如装备监控、流程优化、工艺控制、器件建模、光罩数据校正、版图验证等等。

随着摩尔定律带来的集成电路器件持续微缩,需要在晶圆片上制作出更小尺寸的图形,这对晶圆图案化(Wafer Patterning)带来极大的挑战,而其中光刻技术是晶圆图案化的主要手段。但随着工艺制程的进步,其实早在 180 纳米技术节点上,随着光学图像失真的日益严重光刻机的光学图像分辨率就已经跟不上工艺的发展了。为了补偿光学图像失真,业界引入了光学邻近校正(OPC)技术来补偿光学畸变效应。

实现 OPC 的方法主要有基于规则的 OPC(Rule-Based OPC)和基于模型的 OPC(Model-Based OPC) 两种。早期的基于规则的 OPC, 由于其简单和计算快速的特点被广泛使用。然而这种方法需要人为制定 OPC 规则,随着光学畸变加剧,这些规则变得极为庞杂而难以延续。这时基于模型的 OPC(Model Based OPC)应运而生。传统的基于模型的 OPC 需要精准的光刻建模,一般包含光学建模和光刻胶建模两个部分。通过光刻胶模型可以把光学图像转换为光刻胶图形,而光刻胶模型直接决定了模型的精准度。

过去十年来,计算机技术的进步使得深度学习大放异彩。卷积神经网络(CNN)已广泛用于图像处理上,OPC 的研究人员也将该技术应用于光刻建模。随着人工智能最新的研究成果不断在 OPC 领域得到应用,从两层神经网络,到迁移学习乃至 GAN,OPC 领域已经成为人工智能应用的试验田。

缺陷检测与人工智能

随着摩尔定律的发展,芯片生产工艺越来越复杂,芯片电路单元的尺寸越小,生产过程中就越容易出现各种缺陷。需要在生产过程中及早发现缺陷,及时排除缺陷原因,丢弃缺陷样本,才能防止缺陷晶粒继续加工,影响良率和生产率。

随着线宽的不断缩小,曾经无害的微小颗粒变成影响良率的缺陷,使得检测与缺陷校正的难度日益增加。同样地,3D 晶体管的形成和多重工艺技术也带来了细微变化,导致降低良率的缺陷成倍增加。

半导体晶圆的缺陷是多种多样的,包括形貌缺陷(Topography),污染物(Contamination), 晶体缺陷(Crystal Defect)等等。同时,半导体晶圆缺陷的不规则和细微性给晶圆缺陷检测带来了很大的困难。

半导体行业中缺陷检测的方法目前主要有两种:自动光学检测系统(Automatic Optic Inspection , AOI)以及扫描电子显微镜检测系统(Scanning Electron Microscope ,SEM)。

在自动光学检测方面,鉴于晶圆缺陷的不规则性,图像传感器获取图像后晶圆缺陷的目标检测任务在使用传统图像处理算法进行处理时往往无法兼顾所有可能出现的缺陷。而深度学习方法(基于 CNN 的图像识别方法)对于图像分类和目标检测的高性能表现,可以大大提升不规则的缺陷识别率,提升整体系统的性能和速度。

2021 年,著名的半导体设备企业 AMAT 便推出了基于大数据和人工智能的 ExtractAI。据了解,由应用材料公司数据科学家开发的 ExtractAI 技术解决了最艰巨的晶圆检测问题,即:从高端光学扫描仪产生的数百万个有害信号或「噪音」中,迅速且精确地辨别降低良率的缺陷。ExtractAI 技术可将由光学检测系统生成的大数据与可对特定良率信号进行分类的电子束检测系统进行实时连接,从而推断 Enlight 系统解决了所有晶圆图的信号,将降低良率的缺陷与噪音区分开来。ExtractAI 技术能够仅凭借对千分之一样品的检测,即可在晶圆缺陷图上描绘所有潜在缺陷的特征。这样就可以获得一个可操作的已分类缺陷晶圆图,有效提升半导体节点发展速度、爬坡和良率。人工智能技术在大规模量产期间能够适应和快速识别新的缺陷,随着扫描晶圆数量的增多,其性能和效率也在逐步提升。

在电子束方面,KLA 在其 2020 年推出的 eSL10 电子束图案化晶圆缺陷检查系统便导入深度学习算法,将人工智能系统运用于其中。凭借其先进的人工智能系统,eSL10 能满足 IC 制造商不断发展的检测要求,杜绝了对器件性能影响最关键的缺陷。

除了在制造环节的晶圆缺陷检测外,AI 技术也逐渐渗透到了封装测试环节的缺陷检测中。2020 年,KLA 推出了 Kronos1190 晶圆级封装检测系统、ICOS F160XP 芯片分拣和检测系统以及下一代的 ICOS T3 / T7 系列封装集成电路(IC)组件检测及量测系统。新设备采用 AI 解决方案以提高良率和质量并推动半导体封装创新。

总而言之,传统上对光学和电子束缺陷图像的检测需要人工干预来验证缺陷类型。AI 系统学习和适应,能够快速分类和识别缺陷,减少错误,并且不会减缓生产速度。

工艺开发与人工智能

随着芯片从平面结构向三维结构等的升级,新器件新工艺推动着材料创新,人工智能在数据分析、机器学习等方面的强大能力,能够加速半导体工艺的开发过程,从而显著降低研发周期和成本。

目前英伟达开发的 cuLitho 计算光刻库已经获国际半导体设备、半导体制造厂等应用,加速 2 纳米制程的芯片设计和生产开发;泛林集团(Lam Research)通过人工智能加速了深度晶硅刻蚀。

2023 年,Lam 集团在《自然》上发表了一项研究,研究了在芯片制造工艺开发中使用人工智能(AI)的潜力。

为了制造设计的每个芯片或晶体管,经验丰富且技术娴熟的工程师必须首先创建一个专门的配方,概述每个工艺步骤所需的特定参数和排列。在硅晶圆上构建这些纳米尺寸的器件需要数百个步骤。工艺步骤通常包括将材料薄层沉积到硅晶圆上并以原子级精度蚀刻掉多余材料的多个实例。半导体开发的这一重要阶段目前由人类工程师完成,主要使用他们的直觉和「试错」方法。由于芯片设计的每一个配方都是独一无二的,并且有超过 100 万亿种可能的选项可供整合,因此工艺开发可能既费力又耗时且成本高昂,从而越来越减慢实现下一个技术突破所需的时间。

在 Lam 的研究中,机器和人类参与者竞相以最低的成本创建有针对性的工艺开发配方,权衡了与测试批次、计量和管理费用相关的各种因素。该研究得出的结论是,虽然人类擅长解决具有挑战性和开箱即用的问题,但混合人先、计算机后的策略可以帮助解决工艺开发的繁琐方面,并最终加速工艺工程创新。

未来智能集成电路制造将利用工厂中的连接性来推动自动化改进。AI 系统可以处理海量数据集,深入洞察趋势和潜在偏差,并利用这些信息做出决策。

评论