浅谈因电迁移引发的半导体失效

前言

本文引用地址://www.cazqn.com/article/202402/455800.htm半导体产品老化是一个自然现象,在电子应用中,基于环境、自然等因素,半导体在经过一段时间连续工作之后,其功能会逐渐丧失,这被称为功能失效。半导体功能失效主要包括:腐蚀、载流子注入、电迁移等。其中,电迁移引发的失效机理最为突出。技术型授权代理商Excelpoint世健的工程师Wolfe Yu在此对这一现象进行了分析。

1、 背景

从20世纪初期第一个电子管诞生以来,电子产品与人类的联系越来越紧密,特别是进入21世纪以来,随着集成电路的飞速发展,人们对电子产品的需求也变得愈加丰富。随着电子产品的普及,电子产品失效率越来越高,质量变差,新产品不耐用。

由于产品失效率的提高,许多学者参与到半导体失效分析的研究中。经过大量研究分析和仿真,学者总结出:由于电流的作用,导致导线中的金属原子与电子通过摩擦产生电迁移位移现象所引发的失效是电子产品失效模式的主要因素之一。电迁移满足失效分布函数曲线,产品失效模式与产品工艺、工作温度关系密切。

2、 相关理论

电迁移现象主要发生在半导体在通电状态下,由于电场作用,原子在与电子流的带动下,由于摩擦,产生移位现象,这一现象被称为电迁移。

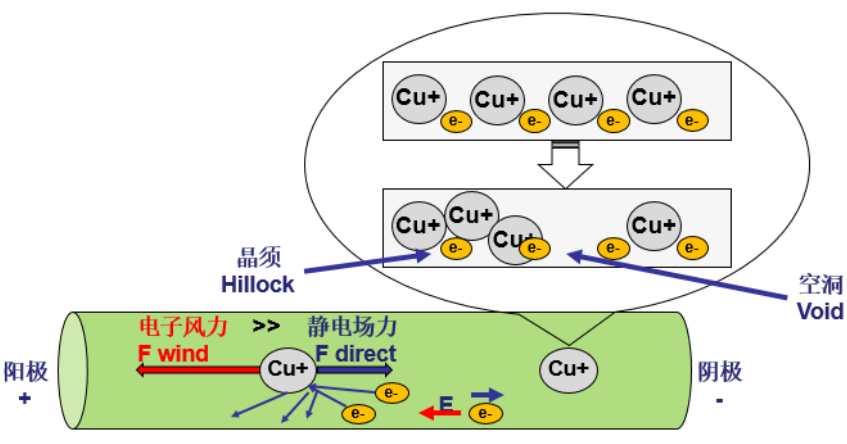

图 1. 电迁移作用力引发半导体失效原理

如图所示,在电场作用下,半导体在导通过程中,正电荷会同时受到静电场力和电子高速运动冲击所产生的风力作用。

由于电流密度增大,电子产生的风力会大于静电场力,从而导致正电荷——也就是金属原子,产生移位,这一现象称为电迁移效应或电迁移现象。经过长期积累,半导体的部分连接就会形成不连贯的晶须(Hillock)或空洞(Void),最终导致半导体元器件失效。

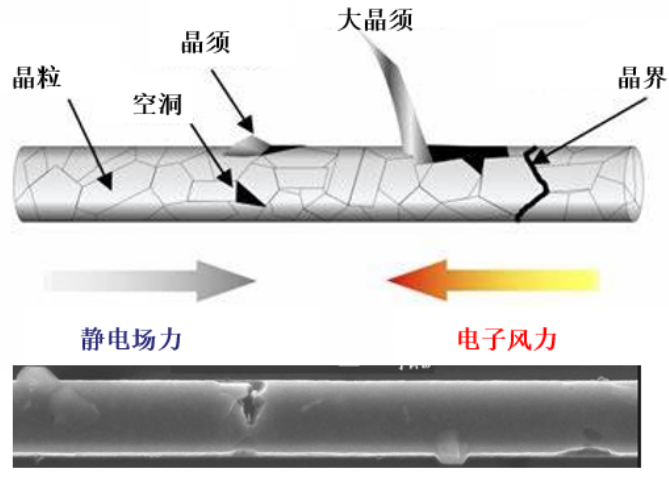

图 2.电迁移作用失效示意图

James R.Black最早在1967年提出基于电迁移引起平均失效时间(MTTF)的数据拟合经验模型,为失效分析具有里程碑的意义。

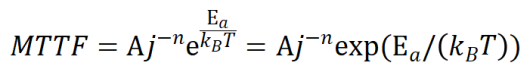

按照Black模型公式:

半导体元器件的失效机理与材料、电子碰撞间隔平均自由时间、有效散射横截面积的因素常量A,电流密度j,绝对温度T等因素相关。Blench和Korhonen等人进一步对电迁移物理模型进行完善。半导体元器件的失效机理单元模型寿命可靠度函数符合欧拉公式。

根据以上公式,电流密度越大,半导体元器件的响应速度就快,元件寿命就会越短,反之,元件的寿命就会增长。要满足半导体元器件的响应速度,则半导体就需要较高的参杂度,另一方面,通过掺杂不同的材料、调整有效散射横截面积等因素也会对芯片的寿命产生影响。

3、 常规解决方案

(1) 报废机制

企业通常利用产品生命周期管理方式,通过对产品生命周期进行分析,为产品设计一个报废界定时间。在汽车、水电气表等行业采用这种方式比较常见。

(2) 系统冗余

在保障性系统设计中,企业一般在报废机制的基础之上,还会通过采用双备份冗余设计、或者K/N表决冗余,并加上系统修复的方式进行系统设计。

4、 技术源头控制

(1) 工艺控制理论

根据Black模型理论,当半导体采用宽线径工艺,横截面积较大时,其芯片寿命会变长,产品平均失效时间MTTF会相对拉得更长。这也从侧面解释了为什么传统工艺设计出来的产品可靠性更高。

(2) 差异化技术控制方法

在芯片原理设计中,采用不同的拓扑架构模型,通过差异化技术实现不同的控制方法也很常见,比如采用CMOS基本单元替代TTL基本单元、采用恒流源替代恒压源来完成不同的产品拓扑模型。在ADC、DAC、运算放大器、比较器等模型设计中十分常见。

在一些设计场合,通过调整芯片输入阈值,降低芯片灵敏度,或通过控制芯片切换频率,降低电流密度,达到提高产品可靠性的目的。

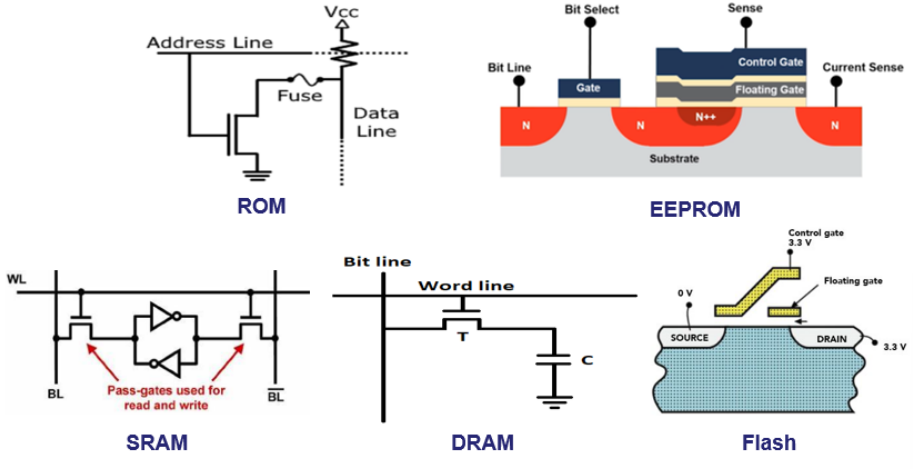

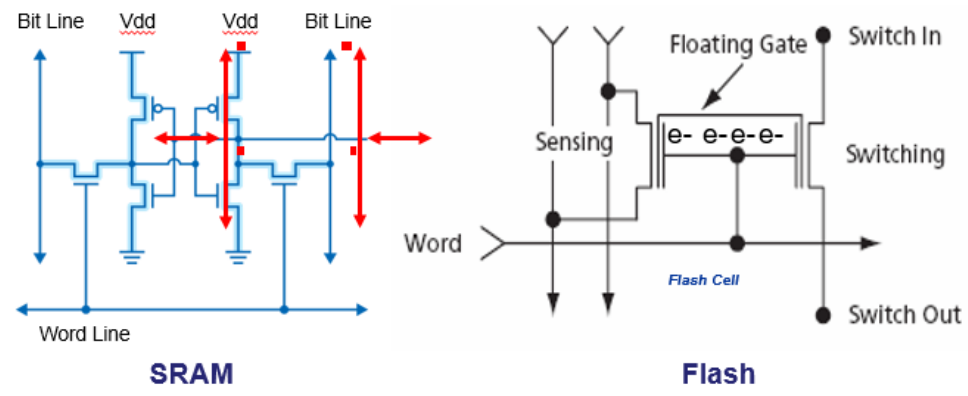

在核心处理芯片模型设计中,根据不同的应用场景,为了追求产品处理速度和可靠性,通常会采用不同的工艺模型进行芯片架构设计,比如从CMOS衍生出来的SRAM、DRAM、ROM、EEPROM、Flash等工艺用于不同的处理器产品架构中,会达到出不同的可靠性效果。

图 3.不同工艺模型芯片单元架构

ROM工艺的处理器是一种非常古老的工艺产品,只能烧录一次,虽然在某些应用场景还依然被大量使用。但在目前主流的产品方案应用中,基于SRAM和Flash工艺的MCU、MPU或FPGA处理器占据了绝大多数应用场景。

5、 Microchip高可靠性Flash FPGA介绍

SRAM工艺的处理器是通过CMOS内部管道切换的方式工作,其产品处理速度较高,被众多用户接受。但是,CMOS工艺有一个致命缺陷,由于工艺原因,伴随CMOS工艺制成芯片产生米勒效应极其容易受到外界干扰,产生翻转。另外,CMOS在翻转过程中,内阻变小,电流密度过大,芯片长期在高电流密度下工作,会加速产品老化时间。

除了基于传统CMOS的SRAM处理器之外,Microchip推出了一种基于叠栅MOS工艺的Flash架构FPGA处理器。

图4.Flash架构FPGA与SRAM架构FPGA的差别

Microchip的FPGA 产品范围覆盖从低端到中端应用,其产品特点以抗单粒子翻转、安全、低功耗和上电即工作著称,广泛应用于通信、国防和航空、工业嵌入式产品。Microchip 目前主推三大系列 FPGA:

·支持5K-150K LE(Logic Elements)具有大量资源的低密度器件的IGLOO®2 系列;

·支持5K-150K LE具有大量资源和 32 位硬核处理器内核(ARM Cortex-M3)的SmartFusion®2 SoC系列;

·以及采用 28 纳米工艺技术实现, 支持25K - 480K LE的高性能PolarFire™ FPGA 和 PolarFire™ SoC系列(Hard 5-Core RISC-V 600MHZ CPU)。

这三大系列FPGA除了具有抗干扰、低功耗、上电启动的特征外,还具有强大的DSP/数学模块(18x18乘法器),可用于当前热门的AI市场。

Microchip的这款Flash架构的FPGA最大的一个特点是电流密度小、抗干扰能力强、动态切换不会出现电流波动,基于其低功耗的特点,可大大延长产品使用寿命。非常适合应用在高可靠性、低失效率应用场合,能高效改善因电迁移引发的半导体失效问题。其授权代理商Excelpoint世健可提供技术支持和指导。

关于世健——亚太区领先的元器件授权代理商

世健是完整解决方案的供应商,为亚洲电子厂商包括原设备生产商(OEM)、原设计生产商(ODM)和电子制造服务提供商(EMS)提供优质的元器件、工程设计及供应链管理服务。多次被权威杂志和行业机构列入全球领先分销商榜单。

世健与供应商及电子厂商紧密协作,为新的科技与趋势作出定位,并帮助客户把这些最先进的科技揉合于他们的产品当中。世健分别在新加坡、中国及越南设有研发中心,专业的研发团队不断创造新的解决方案,帮助客户提高成本效益并缩短产品上市时间。世健研发的完整解决方案及参考设计可应用于工业、无线通信及消费电子等领域。

世健拥有超过35年历史、逾700名员工,业务扩展至亚太区的49个城市和地区,遍及新加坡、马来西亚、泰国、越南、中国、印度、印度尼西亚、菲律宾及澳大利亚等十多个国家。1993年,世健在香港设立区域总部——世健系统(香港)有限公司,正式开始发展中国业务。目前,世健在中国拥有十多家分公司和办事处,遍及中国主要大中型城市。凭借专业的研发团队、顶尖的现场应用支持以及丰富的市场经验,世健在中国业内享有领先地位。

评论