Verilog HDL基础知识6之语法结构

虽然 Verilog 硬件描述语言有很完整的语法结构和系统,这些语法结构的应用给设计描述带来很多方便。但是 Verilog是描述硬件电路的,它是建立在硬件电路的基础上的。有些语法结构是不能与实际硬件电路对应起来的,比如 for 循环,它是不能映射成实际的硬件电路的,因此,Verilog 硬件描述语言分为可综合和不可综合语言。下面我们就来简单的介绍一下可综合与不可综合。

本文引用地址://www.cazqn.com/article/202402/455549.htm(1) 所谓可综合,就是我们编写的Verilog代码能够被综合器转化为相应的电路结构。因此,我们常用可综合语句来描述数字硬件电路。

(2) 所谓不可综合,就是我们编写的 Verilog 代码无法综合生成实际的电路。因此,不可综合语句一般我们在描述数字硬件电路时是用不到的,不过,我们可以用它来仿真、验证我们描述的数字硬件电路

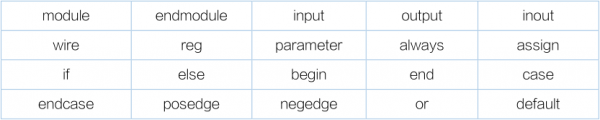

Verilog的关键字

由于我们是将 Verilog 用于描述数字硬件电路,所以我们只需要掌握可以被综合器综合的那部分关键字就可以了。下面我们列出了常用的可综合关键字,如下。

首先我们介绍的是 module 和 endmodule,它们是成对使用的,模块是 Verilog 设计中基本功能块,一个最简单的模块是由模块命名、端口列表两个部分组成。整个模块是由 module 开头,endmodule 结尾,module 后面紧跟着的是模块名,每个模块都有它自己的名字。

input、output和 inout 用于端口定义,wire 和 reg 是用来声明数据类型,parameter 是用来声明参数类型,always 是过程赋值语句,assing 是连续赋值语句。

if 和 else 成对使用,是条件判断语句,和 C语言中的 if 和 else 是一样的功能,begin 和 end 也是成对使用,相当于 C 语言中的大括号。

case、endcase 和 default 成对使用,是一个多分支条件语句,和 C 语言中的 switch 一样的功能。

posedege、negedge 和 or 这三个关键字是和 always 关键字联合使用的,posedge 是上升沿触发,negedge 是下降沿触发,posedge or negedge 是既有上升沿又有下降沿。在Verilog中,注意关键字使用小写。

Verilog的基本程序框架

Verilog 是一种用于数字逻辑电路设计的语言,我们以数字电路中最简单的与门为例,来作为入门学习的第一个程序。与门的 Verilog 代码如下。

module yumen

(

a, b, c

);

input a;

input b;

output c;

assign c = a & b;

endmodule

下面我们就来简单的介绍一下这个代码,在这个代码中,a 和 b 是与门的输入,c 是与门的输出,也就是说,该代码实现了一个 2 输入的与门电路。这里我们需要说明的是,大家不必过分去苛求细节的语法,只要着眼于基本程序框架就行。通过上面的程序我们给大家总结如下:

1.Verilog HDL 程序是由模块构成的,每个模块的内容都是嵌在 module 和 endmodule两个语句之间。

2.每个模块要进行端口定义,并说明输入输出口,然后对模块的功能进行行为逻辑描述。

3.Verilog HDL 程序的书写格式自由,一行可以写几个语句,一个语句也可以分写多行。

4.除了 endmodule 语句外,每个语句和数据定义的最后必须有分号。

评论