ST和GlobalFoundries在法国Crolles附近的新工厂联合推进FD-SOI

意法半导体(ST)和GlobalFoundries (GF)刚刚签署了一份谅解备忘录,将在意法半导体位于法国Crolles的现有晶圆厂旁边新建一座联合运营的300毫米半导体晶圆厂。新工厂将支持多种半导体技术和工艺节点,包括FD-SOI。ST和GF预计,该晶圆厂将于2024年开始生产芯片,到2026年将达到满负荷生产,每年生产多达62万片300毫米晶圆。

本文引用地址://www.cazqn.com/article/202208/437510.htm法国东南部的Crolles,距离意大利边境不远,长期以来一直是FD-SOI发展的温床。从许多方面来看,FD-SOI是一种技术含量较低的方法,可以实现FinFETs和GAA fet的一些优势,包括更高的速度、更低的功耗,以及由于导电沟道完全耗尽(未掺杂),芯片上晶体管与晶体管之间的参数变化更小。更少的片内参数变化意味着ic设计人员可以减少所需的设计裕量(包括电源电压和时序),从而提高芯片速度,并通过降低所需的工作电压来降低功耗。

加州大学柏克莱分校的胡正明博士和他的团队早在1999年就根据DARPA的合约开发了FinFETs。DARPA取消了这份合同,因为很明显,平面场效应晶体管在运行了半个世纪后,随着尺寸越来越小,最终会耗尽气体。DARPA寻求替代方案。

小型平面FET存在短沟道泄漏问题,这使得FET无法完全关断。FinFET相对于平面FET的优势在于fin FET架构在FET沟道的四个边中的三个边周围构建了栅极。这种布置允许来自栅极的电场更深地穿透到FET的传导沟道中,这减少了短沟道泄漏,并且允许更好地控制通过沟道的电流。

随着平面FET尺寸的缩小,短沟道泄漏的幅度增加,导致功耗和散热挑战增加,并迫使半导体制造商采用FinFETs。早在2011年,英特尔就是第一家将finfet用于其22纳米工艺节点的商业半导体公司,这比finfet的首次开发晚了十多年。FinFETs目前几乎普遍用于采用20nm工艺节点或更新工艺节点制造的芯片。

然而,FinFETs现在已经没有气体了。驱动FinFET晶体管栅极的三个边不再能实现所需的速度和低漏电流。我们现在必须驱动FET栅极的所有四个边,以获得性能良好的晶体管。进入GAAFETs,它已经在三星的3纳米工艺节点的晶圆厂生产。英特尔和TSMC也将分别为其英特尔20A和N22纳米节点使用砷化镓场效应晶体管。三星将其GAAFETs称为“多桥沟道fet”(MBC fet);英特尔称它们为“带状场效应晶体管”;TSMC称之为纳米片状砷化镓场效应晶体管。

像FinFETs一样,GAAFETs是3D结构。GAAFET传导通道不是由鳍片构成,而是由未掺杂的硅纳米线、纳米片或纳米带构成,这些纳米线、纳米片或纳米带非常薄,基本上是2D结构,采用原子层沉积(ALD)等先进工艺技术制成。这些纳米级导电沟道完全被GAAFET的栅极结构所封装。

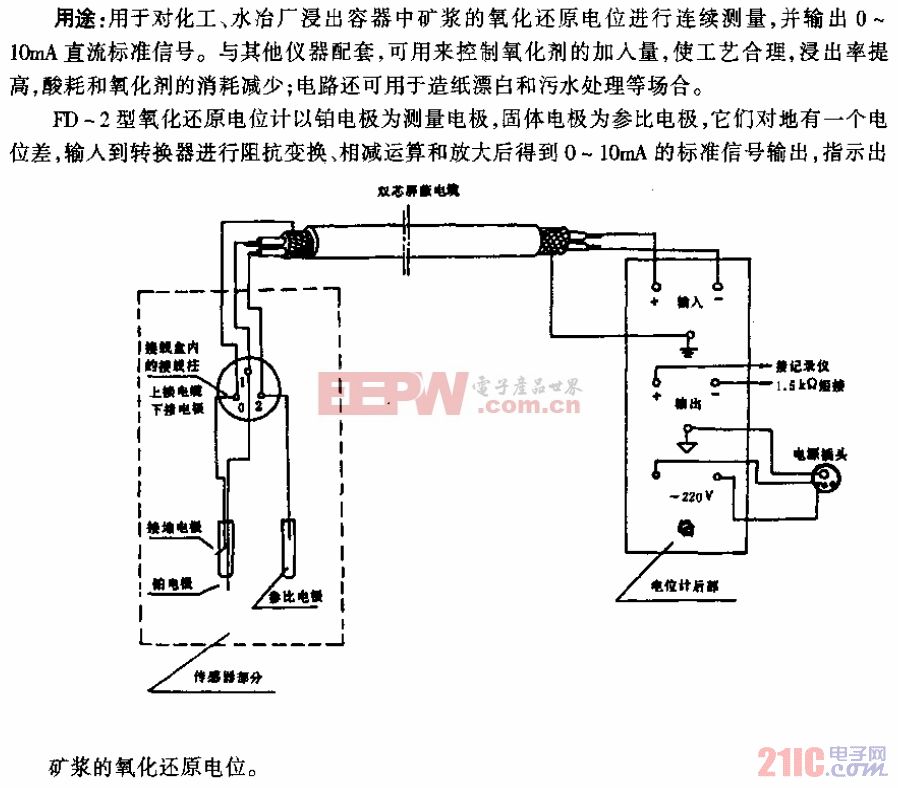

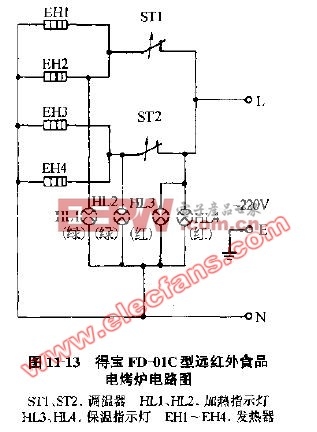

FD-SOI FET的超薄导电沟道不会遭受与体硅制成的平面FET相同的泄漏效应。图片来源:意法半导体。

FD-SOI fet具有本质上是2D传导沟道的东西,通过在薄的生长的二氧化硅绝缘层上结合或施加非常薄的、非常均匀的硅层来创建。如果FD-SOI FET的导电沟道足够薄,则位于导电沟道顶部的晶体管栅极的电场会完全穿透沟道,因此不需要像GAAFETs那样在所有四个侧面包围沟道的栅极结构。

除了FD-SOI衬底之外,FD-SOI fet以类似的方式制造,并且使用与制造平面fet相同的设备。GAA结构更复杂,需要使用昂贵的EUV光刻技术来制造所需的小结构。像FinFETs和GAA fet一样,FD-SOI fet没有短沟道泄漏问题,并且它们不像GAA fet那样需要EUV光刻。因此,你可以称FD-SOI晶体管为“几乎全栅场效应晶体管”(GAAAFETs)。你可能会,但没人会。

一个有趣的巧合是,由胡正明博士领导的同一加州大学伯克利分校团队在1999年根据DARPA合同开发了FinFET,同时根据同一DARPA合同开发了非常类似于FD-SOI FET架构的东西。胡把这第二种FET结构称为UTBSOI(超薄绝缘体上硅)。

与平面MOSFETs相比,FinFETs、GAAFETs和UTBSOI FETs具有许多优势:

更好的信号摆幅

对栅极长度和漏极电压不太敏感

没有随机的掺杂剂波动,因为FinFETs鳍片、GAAFETs中的纳米结构导电沟道和UTBSOI/FD-SOI fet中的薄导电沟道都是完全耗尽的——它们没有掺杂

较高的导通电流和较低的泄漏

更低的Vdd和更低的泄漏,因此功耗更低

在FinFETs或GAAFETs和ut bsoi/FD-SOI fet之间至少有两个重要的区别。首先,在FD-SOI FET的沟道下方添加反向偏置相对容易,这是通过晶圆上薄绝缘层下方的体硅衬底实现的。反向偏置允许您调整FET阈值电压,调整性能和功耗。如果你决定变得非常奇特,你可以通过使用每个晶体管下的硅作为第二个栅极来调整芯片上的单个场效应晶体管。向FinFETs或GAAFETs添加反向偏置并不容易。第二,相对于FinFETs或GAAFETs,FD-SOI不会得到更小的晶体管,因此不会实现相同的晶体管密度。这是不需要昂贵的EUV光刻术的另一面。

FD-SOI处理仍然比传统的平面IC处理昂贵,因为它需要特殊的FD-SOI晶片。它只是没有制造小型FinFETs和GAAFETs所需的EUV光刻和其他3D处理技术昂贵。传统的IC制造使用比FD-SOI晶片便宜得多的体硅晶片。FD-SOI晶片的主要供应商是位于Bernin的Soitec,它就在格勒诺布尔北部意法半导体Crolles fab complex的街道上。

巧合的是,Soitec、GF和ST以及CEA(法国替代能源和原子能委员会)在今年早些时候宣布了一项合作协议,共同定义FD-SOI行业的下一代路线图。在该公告中,CEA主席Franç ois Jacq表示:“CEA与意法半导体、Soitec和GlobalFoundries有着……长期的R&D深度合作历史,并且一直非常积极地参与由欧盟委员会和成员国领导的旨在为FD-SOI建立完整生态系统的倡议,该生态系统包括材料供应商、设计公司、EDA工具提供商、无晶圆厂公司和最终用户。”这些是构成FD-SOI“平台”的元素

7月份的ST/GF FD-SOI备忘录公告还称,“ST和GF将获得法国政府对新设施的重大财政支持。该工厂将为欧洲芯片法案的目标做出巨大贡献,包括欧洲到2030年达到全球半导体产量20%的目标。”这一声明是欧洲对美国政府的一记猛击,美国政府似乎在该国自己的芯片法案上拖后腿,这让英特尔和TSMC等公司非常懊恼。然而,美国参众两院上周最终通过了该法案,预计美国总统乔·拜登将于本周签署该法案使之成为法律。

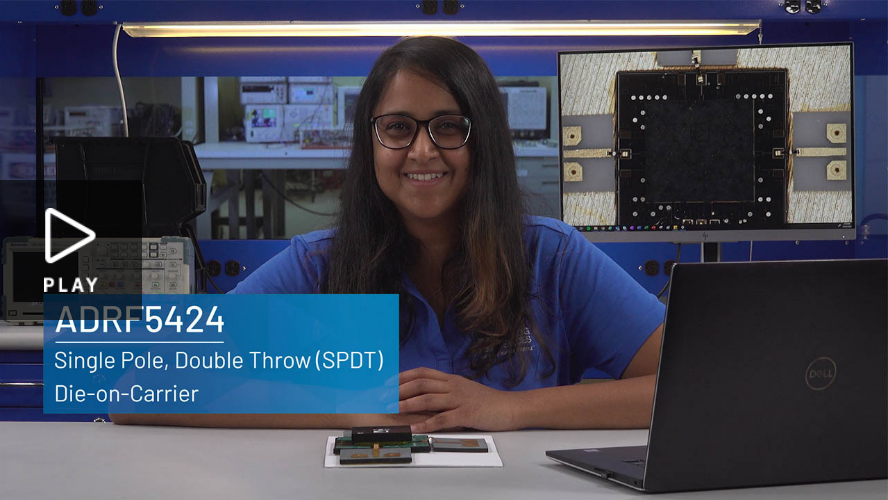

看来法国正在大力发展FD-SOI,如果你不打算从ASML购买1.5亿美元的EUV踏步机或下一代3亿美元的“高NA”EUV踏步机,这是一个不错的战略。FD-SOI将FinFET和GAAFET的许多优点赋予了一个便宜得多的工艺节点。GF已经提供了两种FD-SOI工艺节点或平台,称为RF SOI和22纳米FDX22。今年5月,GF发布了一个名为GF Connex的RF元平台,该平台整合了该公司RF SOI、FDX、SiGe和FinFET半导体平台的元素,以满足智能移动和物联网设备以及通信基础设施设备的各种通信需求。

就其本身而言,ST目前提供28纳米FD-SOI工艺/平台。28纳米节点是目前业内最具成本效益的工艺节点,因此使用该节点有很多经济效益。然而,技术不可避免地在前进,Crolles联合声明提到了18纳米ST工艺技术。这似乎与ST的技术、制造、质量和供应链总裁Orio Bellezza在今年5月题为“技术与制造”的意法半导体资本市场日演讲中讨论的嵌入式PCM(非易失性相变存储器)18纳米FD-SOI工艺技术相同。

ST、GF和CEA的联合声明巩固了FD-SOI在未来几十年特定应用中作为GAAFETs可行替代品的地位,包括汽车、物联网和移动市场中的应用。对于这些应用,重要的不是晶体管的数量;这就是那些晶体管能做的

评论