从抗辐射到耐辐射:如何打造强韧耐辐射系统

微电子或集成电路 (IC) 是许多前沿应用的核心,其工艺进步直接影响各种应用的创新。但在机器人、太空探索、航空航天、核电站、精密检测、医学成像、甚至环境保护和食品安全等应用中,工艺的先进性并不是全部,“辐射”是这些领域的 IC 需要解决的核心问题。辐射可能会导致机器人发生故障,使医学成像不准确,或者工业应用机器出现停转等等。

本文引用地址://www.cazqn.com/article/202111/429731.htm对于 IC 设计师来说,在所有上述应用中,宇宙空间应该说是最具挑战性的应用场景。失去地球大气层的保护,电子系统在阿尔法 ( Alpha ) 和贝塔 ( Beta ) 粒子、伽马 ( Gamma ) 和 X 射线以及银河宇宙辐射等高能(电离)辐射面前,相当脆弱,所以能够抗衡此类辐射的航空级IC 代表了防辐射IC 技术的塔尖。

电离辐射有足够的能量让电子脱离轨道。如果这个电子代表存储器中的一个数位或总线接口上的一个值,该值就可能被改变或“翻转”。这种状况有多种叫法,包括单粒子效应 (SEE)、单粒子翻转或单粒子闩锁。无论具体叫什么,如果错误的数位发生翻转,例如应用代码中的指令或寄存器中的控制数位,整个系统就会崩溃。

耐辐射 (Radiation-tolerant)和抗辐射加固 (Radiation-hardened)的区别

为了在宇宙空间中运行,电子系统需要具有防范辐射风险的能力。某些 IC 制造商采用标准半导体晶圆中加入防护衬底的方式提供“ 加固 ( hardened ) ”组件。虽然抗辐射加固 IC 具有更强的耐辐射能力,但却不能彻底免疫。与此同时,因为抗辐射芯片设计要求更复杂且产量更低,因而价格也明显更加昂贵。

此外,即便所需要的组件可以被设计成抗辐射加固IC,因为其投产速度的滞后性,也阻碍了航天器设计人员对抗辐射加固 IC 选用。

在遭遇电离辐射时,除了采用抗辐射加固IC的设计方法提供抗辐射能力,设计人员还可以通过运用器件和设计方法进行检测并予以纠正。

这就是所谓的耐辐射。

这种方法的主要优势在于,可以将大量组件都制作成耐辐射组件。例如,众多存储器技术采用纠错码技术来检测和纠正存储器内的位翻转。

三重模块冗余

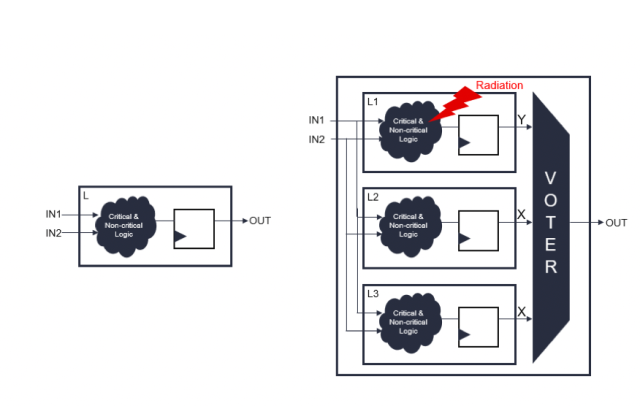

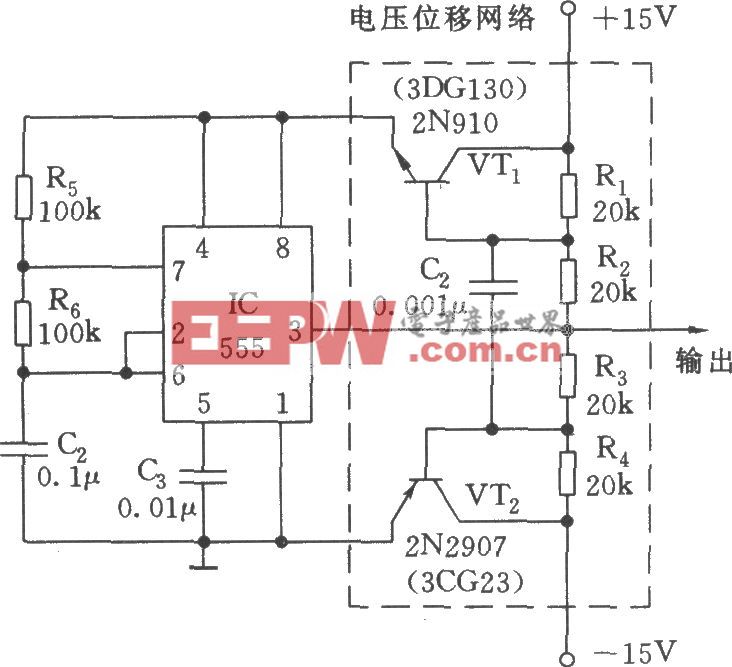

如果寄存器内发生了位翻转,或由存储器检索的数据在总线接口传输的过程中发生了翻转,对此类事件进行检测则极为复杂。开发者通常使用三重模块冗余技术 (triple modular redundancy, TMR)来检测和纠正此类性质的事件。通过TMR,主要电路采用完全相同的设计提供并行三冗余,由“票决”电路比较这些相同路径的输出,按少数服从多数的原则决定输出。(参见图 1)

如果其中一条电路遭遇影响输出的事件,其输出将不同于其余两条电路的输出。如果只使用两条完全相同的电路进行比较,输出不同将提示有事件发生,但无法辨别具体发生在哪条电路上。

哪个输出是正确的?使用三条电路,可以确定正确的输出(可以进行合理假设,在两条电路上发生完全相同的 SEE 的概率基本为零)。

开发者随即可以采纳多数输出或重新评估设备运行。大量 OEM 厂商对自己的设计采用定制 IC,因此为了实现 TMR,他们在电路板上并行布局 IC 的三个副本并追加一个投票器 IC。

图1 采用三模冗余的情况下,使用“票决”电路对并行的三个相同的电路开展评估,确保电路产生正确(大多数)输出

任务关键型 TMR

TMR 在对系统性能影响最小(指时延)的情况下提供高度的可靠性。然而,这种可靠性显然有其代价。它增大了系统的占板面积、功耗和费用。鉴于各条电路的重要性并不均等,理想情况下,开发者希望仅在必要时使用 TMR。

以温度传感器为例。不常发生的数据点错误不会影响整体监测性能,因为样本可以随时间平均,因此不必承担三个传感器或三个监测电路带来的附加费用。

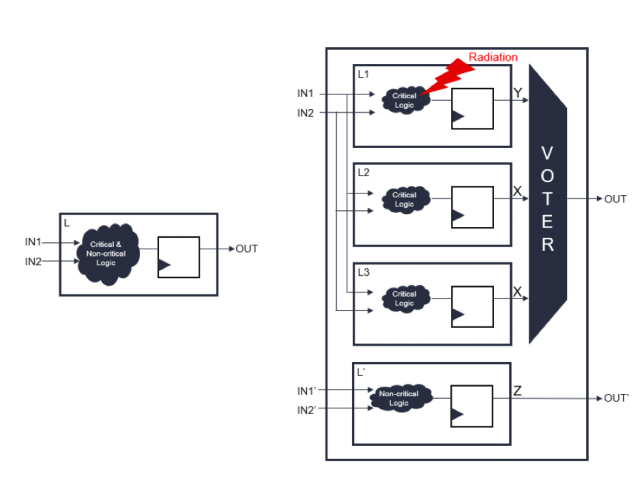

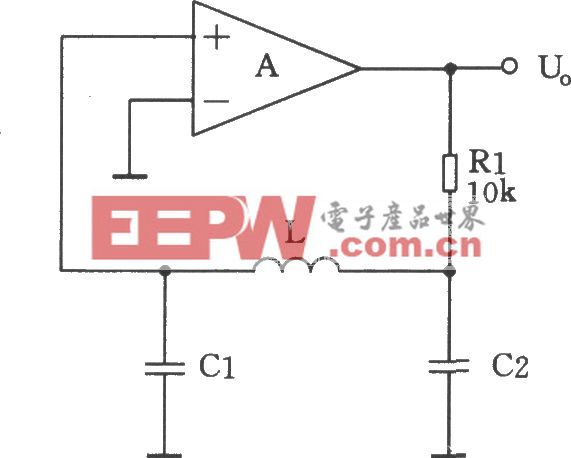

除了在电路板上为电路创建三个副本以外,还有一种替代方法是在赛灵思 XQR Versal ACAP或自适应 SoC 等航天级可编程器件中实现电路。赛灵思软硬件一体化可编程逻辑方法让设计人员能够在单个芯片中实现复杂的 TMR。无需并行布局三个 IC,单个可编程逻辑器件就能将三条电路和票决电路集成在一起。(参见图 2)

图2 如图所示的赛灵思 XQR 航天级器件能将使用 TMR 的任务关键型电路实现在单个芯片中

使用可编程逻辑的主要优势在于设计人员能够根据需要实现 TMR。借助这种方法,任务关键型模块能够在无需复制非重要模块的情况下,以最高可靠性实现,从而避免推高成本和功耗。

此外,因为 ACAP 或 FPGA 中的自适应系统并非定制 IC 那样在功能上是固定的,所以设计人员在推出新特性时可以避免因重新开发新 IC 而造成的延误或成本。

随着 AI 和机器学习技术不断演进发展,成为电子系统不可或缺的组成部分,自适应灵活性也正在变得越来越重要。这意味着当新的 AI 推断模型出现时,就可以通过软件更新的方式来更新硬件系统。此外,这种更新还能用于在轨系统,在部署后进一步提高它们的效率和性能。这是直到近期才具备的功能。

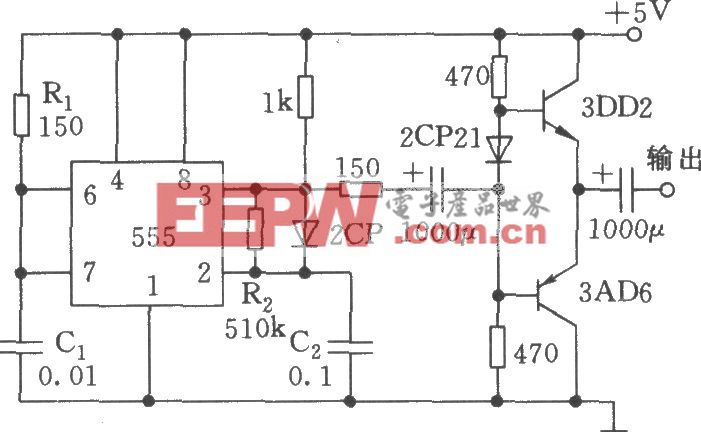

擦除

可编程逻辑和定制 IC 之间的差异在于 ACAP/FPGA 需要配置。通过配置,可以定义可编程器件的功能。配置数据存储在基于 SRAM 的单元中,也被称作配置 RAM 或简称 CRAM。因此,CARM 可能受辐射事件的影响,可能会改变可编程器件的既定“特性”。

擦除是一种用来保护配置存储器单元的方法。器件有专门一部分通过使用校验和分析,不断对 CRAM 做逐帧检查。如果检测到辐射事件,就启动重配置。器件“擦除”(即重新加载)被电离辐射损坏的配置帧。在纠正辐射事件后,再继续处理。

需要注意的是,只有受影响的帧才需要擦除,整个系统则继续不中断地运行。此外,ACAP/FPGA 也能采用“盲擦除”。在采用盲擦除时,器件不会检查是否有辐射事件发生,而是通过定期进行重配置,确保其处在已知的良性状态下。这种方法非常可靠,因为它强制刷新 CRAM,甚至是在非必要时。

在之前的几代产品中,赛灵思 CRAM 防范单事件翻转的擦除机制是通过外接 IC实现的,而如今,该功能已经作为一项功能,集成在 FPGA 的可编程逻辑中,或 ACAP 的专用处理器中。

就其本质而言,电子产品不具备与生俱来的耐辐射能力。但是却可以通过先进的设计方法,让系统自动识别并改变辐射事件,提高系统的总体耐辐射能力,从而大幅提升可靠性和恢复能力。通过采用自适应平台,设计人员可以运用三重模块冗余技术和擦除技术,优化系统成本,降低占板面积和功耗。

评论