AI与机器学习发展迅速,FPGA可提供高能效和灵活性

1 为什么AI/ML发展如此迅速?

多年来,人工智能(AI)/机器学习(ML)市场一直以指数级的速度快速增长,其解决方案遍布我们周围,从机器人和其他机械系统的预测故障算法、电子商务中的购买行为建议、自动驾驶车辆的目标检测、电子交易中的风险缓解到DNA测序等等,我们身边有各种各样的解决方案,示例不胜枚举。

那么,为什么AI/ML发展如此迅速呢?

据IDC、Gartner和其他市调机构的分析,全球大约80%的数据是非结构化数据。电子邮件、照片、语音邮件、视频和许多其他数据源每天都在堆积。无论是优化行业或企业的流程、预测消费者的消费趋势和兴趣、增强金融系统的安全性、维护合规性等等,这些数据都具有价值。AI/ML不仅在数据清理(从非结构化数据创建结构化数据)方面扮演着重要角色,而且在数据分析方面也发挥着关键作用。

在过去10年中,汽车市场一直在改进自动驾驶车辆,并且中国和美国都进行了现场试验。中国吉利汽车集团在其驾驶辅助和完整的自动驾驶车辆产品线上投入了大量资金,这些都是由AI/ML支持的。工业4.0和5.0在很大程度上依赖AI/ML算法来实现其机器人技术和流程自动化。在医学领域有许多用例,包括成像、疾病预测、诊断和患者病历维护等。

1)数据加速市场

当工作负载增加时,早期的数据中心架构依赖于添加更多的服务器。随着时间的推移,数据中心的计算节点增加到数千、数万,甚至在某些情况下增加到十几万个,因此占用空间、电力消耗和降温成为一种负担。网络的运营商都在寻找全新的、更高效的方法来处理数据。

数据加速器主要是使用图形处理器(GPU)实现的,用于处理繁重的数学工作负载。高性能计算(HPC)、基因组学、人工智能(包括训练和推理)和许多其他用例都利用了这种协同处理数据加速。总的来讲,我们现在有专用集成电路(ASIC)、GPU和现场可编程逻辑门阵列(FPGA)解决方案来争夺这个数据加速市场。随着我们不断向边缘技术发展,数据加速器的灵活性和最佳的性能效率将成为制胜关键技术。

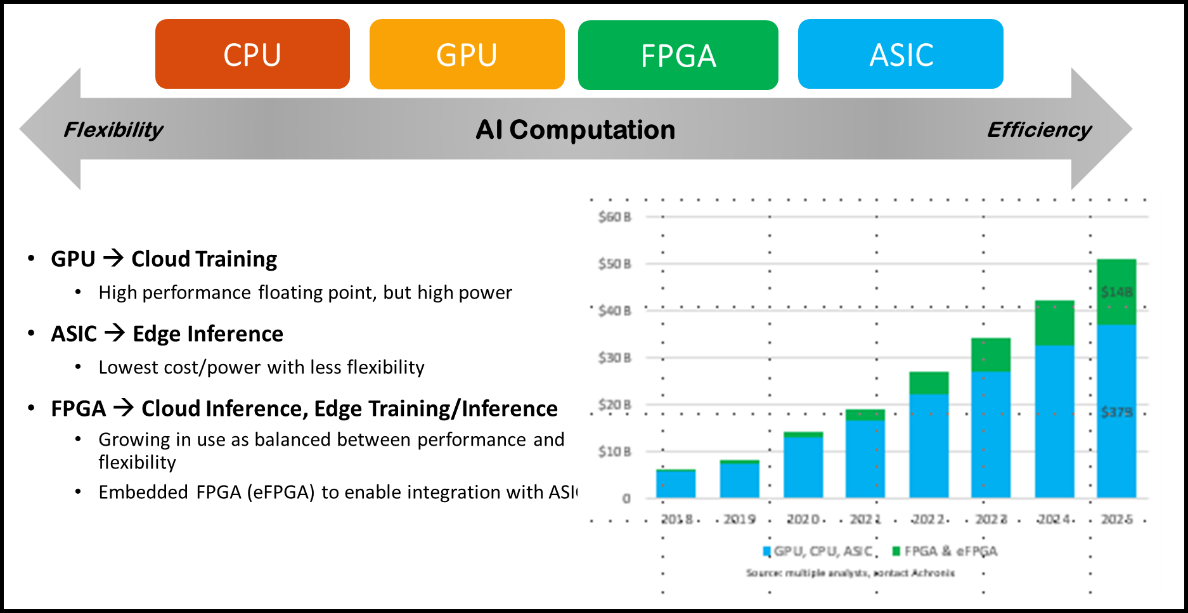

从图1这个图表可以看出:中央处理器(CPU)总是拥有最高的灵活性,但需要权衡功耗和成本;当我们在探讨用“老派”方法来应对核心数据中心中增加的工作负载时,我们自然就会注意到这一点;这样剩下可用的解决方案就只有GPU、ASIC和FPGA了。ASIC肯定会提供最高的效率,但是ASIC的功能是固定的,无法提供所需的灵活性,以适应不断变化的AI算法、新技术的规格变化、供应商特定的要求和工作负载优化。

GPU是核心数据中心的原始主力,仅限于处理纯计算用例,在大多数情况下不具备加速网络和存储的能力,而且这样做是以牺牲功耗和成本为代价的。FPGA能够进行网络、计算和存储加速,具有ASIC级的处理速度和所需的灵活性,能够为当今的核心和边缘数据中心提供最佳的数据加速。

图1 AI/ML计算解决方案的对比

2)神经网络模型与算法

AI/ML有2个主要组成部分,即网络模型训练和用于机器学习的推理。就部署和总体收入而言,市场的绝大部分在于机器学习推理。有许多神经网络模型可以分层来创建各种神经网络或算法。一些更常见的类型包括卷积神经网络(CNN)、循环神经网络(RNN)、转置器、图神经网络和前馈神经网络。ResNet、AlexNet和YOLO是众所周知的CNN,GRU和LSTM是比较常见的RNN,谷歌(Google)的BERT、微软(Microsoft)的Turing NLG和OpenAI的GPT 3.5是transformer神经网络的例子。

当神经网络用于更大的批量处理(Batch size)时,GPU通常表现得更好,并且可以高度并行化处理。FPGA在执行顺序神经网络(RNN是一个很好的示例),以及其他更容易并行计算的模型方面具有更高的灵活性。数据加速器的成功将在很大程度上取决于设备的利用率。GPU在顺序模型中通常会达不到要求,因为它们通常未得到充分利用。这就像购买一辆兰博基尼以每小时20公里的速度行驶一样。

Achronix凭借其完整的FPGA技术组合为机器学习推理应用提供全面解决方案。通过与多个生态系统合作伙伴合作,最终用户可以实现基于FPGA的推理解决方案,无论是使用Speedcore将半导体知识产权(IP)集成到他们自己的芯片设计中,还是使用Speedster7t FPGA独立芯片将FPGA芯片放在他们自己的PCB上,或者使用VectorPath PCIe加速卡进行交钥匙项目(一站式方案)。

Tom Spencer(Achronix产品营销高级经理)

2 工程师或研发人员的挑战

在许多应用中,AI/ML算法因工作负载的变化或对推理神经网络层的优化而发生变化。事实证明,FPGA可提供最佳的能效,同时保持这些不同要求所需的灵活性。尽管ASIC具有最高的性能和能效,但它们可能需要花费长达2年的时间来开发和生产,而且它们不能提供灵活性以适应不同的AI/ML算法。GPU提供了灵活性,但在适应许多不同的算法方面能力有限,而且能效很低。FPGA实现了最快的上市时间,并在平台的全生命周期内提供灵活性。除了FPGA提供的上市时间优势之外,Achronix还通过提供嵌入式IP、芯片级和板卡级的FPGA技术,比其他业界领先的FPGA公司更前进了一步。

Achronix是唯一一家能够同时提供嵌入式FPGA知识产权(业界通常将其称为eFPGA)、独立FPGA芯片和基于该芯片的PCIe加速卡的高性能FPGA独立硬件供应商(IHV)。Achronix提供了开发工具套件,其中包括用于配置、布局和布线以及比特流生成的ACE工具,Synopsys Synpilfy Pro的Achronix特定版本,可用于综合和与仿真工具的互操作。Achronix工具支持在多个流程步骤中使用许多常见的仿真器进行仿真,包括VCS(Synopsys)、QuestaSim(Mentor)、Incisive(Cadence)和Riviera(Aldec)。通过投资Achronix工具套件,用户能够开发多种解决方案,包括使用Speedcore开发具有嵌入式FPGA功能的大批量定制ASIC或SoC,使用Speedster7t器件开发专有PCB子系统,或简单地使用基于PCIe的插卡模式,通过采用VectorPath加速卡来实现。

3 Achronix的解决方案

Achronix为AI/ML计算、联网和存储应用开发了基于FPGA的数据加速产品。与其他高性能FPGA公司不同,Achronix可以同时提供FPGA芯片和嵌入式FPGA IP解决方案。除了FPGA器件和eFPGA IP,Achronix还提供加速卡,可用于开发、现场试验或批量生产。Speedster7t系列FPGA器件是Achronix最新推出的、采用了台积电7nm工艺节点的FPGA芯片。该系列FPGA提供了业内最高速度的I/O接口,具有400GbE、PCIe Gen 5和双存储接口:标准DDR4和GDDR6。与DDR4相比,GDDR6提供了令人印象深刻的600%速度优势。

这些高速接口意味着大量数据可以轻松通过FPGA。Achronix构建了一个二维片上网络(2D NoC),它实际上是联通所有外部I/O、FPGA内固化功能块和FPGA自身具有的逻辑阵列之间的高速公路。这个二维片上网络具有超过20Tbps的双向总带宽,远远超过了I/O和功能模块的总带宽。这消除了由于芯片内部拥塞带来的延迟问题。

对于那些对成本和/或功耗非常敏感的用例,通常会开发ASIC。但是,当您需要前面所讨论的灵活性时,您会怎么做呢?无论是算法的新变体、不断变化的需求、供应商的特定需求、操作人员的特定需求、协议适配还是功能系统模块的不同接口,都需要一定程度的灵活性。Speedcore eFPGA IP是由ASIC开发者和Achronix定义的、具有“刚好足够”灵活性的解决方案。其中LUT、存储器、DSP/MLP和2D NoC之间所需的资源已经确定,然后Achronix向用户提供定制IP,以集成到他们的ASIC或SoC设计中。

VectorPath加速卡可用作评估或开发平台、现场试验工具或用于产品批量生产中,还可以创建该解决方案的定制版本以满足特定的用户需求。

评论