一种基于FPGA的BiSS编码器解码器设计

作者简介:李绍军(1989—),男,硕士,工程师,研究方向为光电云台伺服控制。

本文引用地址://www.cazqn.com/article/202109/428017.htm0 引言

BiSS 协议是一种时钟频率高达10 MHz 的串行通信协议,物理上采用RS422 差分总线方式,使用BiSS 通信协议的光电编码器具有数据线占用少、抗干扰性强、通信速率快等优点,在机器人、数控机床、雷达转台等领域应用广泛[1-2]。一些新型微控制器已经具备了物理上支持BiSS 通信协议的外设接口,如Infineon 公司的XMC4000 系列使用SPI 接口可完成BiSS 协议解码功能[3],但当进行伺服电机控制时需要CPU 在执行FOC 算法的基础上实时通过较复杂的软件实现BiSS 协议解码,增加了CPU的负担;TI 公司的TMS320F3837x 系列使用CLB 模块配合SPI 外设接口实现对BiSS 协议的解码[4],可以减轻CPU 的负担,但CLB 外设数量有限。且这些方式均难以达到BiSS 协议最高时钟频率,综合比较使用FPGA 解码可降低CPU 负担同时可充分发挥BiSS 协议时钟频率高的优点。文中针对BiSS 协议数据帧格式,设计了BiSS 协议解码器状态机和CRC 校验器,并使用Moldisim 对校验过程进行仿真,FPGA 将解码数据发送给DSP,通过驱动永磁同步电机对该设计的解码效果进行了验证。

1 解码器硬件设计

1.1 BiSS协议分析

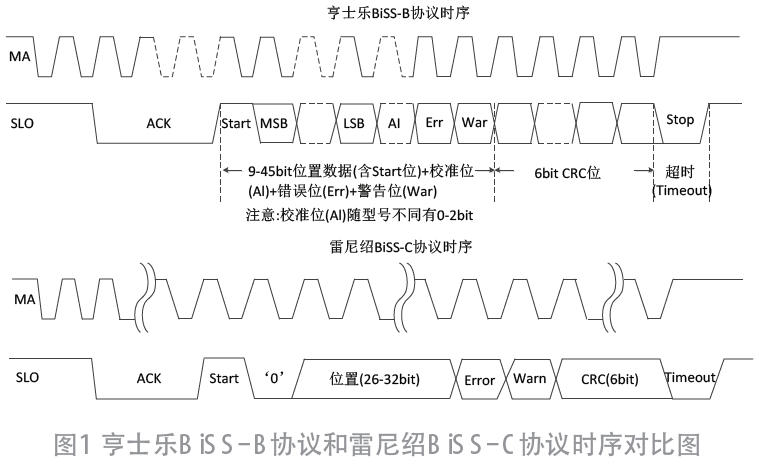

旋转编码器是伺服电机常用的一种位置传感器,常见外部接口形式有RS422、SSI、BiSS 等。使用RS422或者SSI 接口时时钟频率一般低于1 MHz,且受限于总线协议单帧传输位数限制,当需要传输的位置数据位数较多时会导致编码器位置采样频率偏低。另一种常见位置传感器是旋转变压器,随着技术的不断发展,当前旋转编码器更容易实现比旋转变压器更高的分辨率,而BiSS 协议由于时钟频率高,传输位数多,可以轻松实现对位置数据20 kHz 的采样频率,因此使用BiSS 协议的旋转编码器十分适用于动态性能要求高的伺服控制领域。BiSS 协议最初由德国IC-Haus 公司提出,是一种较为新型的开放式同步串行通信总线协议,在提出后很快开发出BiSS-B 协议并得到广泛应用,后由于海德汉公司对BiSS-B 协议的专利诉求,导致很多编码器厂商联合开发出BiSS-C 协议[5-6]。根据工作模式,BiSS 协议可分为传感器模式和寄存器模式,寄存器模式便于使用者掌握更多编码器状态信息,传感器模式与寄存器模式相比传输信息少,因此具有更高的位置采样频率。图1 所示为亨士乐公司BiSS-B 协议编码器时序和雷尼绍公司BiSS-C 协议编码器时序对比图,见文献[7-8]。由图中可见,BiSS-B 和BiSS-C 协议高度相似,均由2 条信号线构成,其中一条为时钟线,另一条为数据线。数据线上均有Ack 位、Start 位、位置数据位、error 位、Warn 位、CRC 校验位和Timeout 位;不同点在于BiSS-C 协议在Start 位和位置数据位间还有额外的1 bit 0 位。

文中就BiSS-B 协议的旋转编码器传感器模式展开讨论。

1.2 硬件电路设计

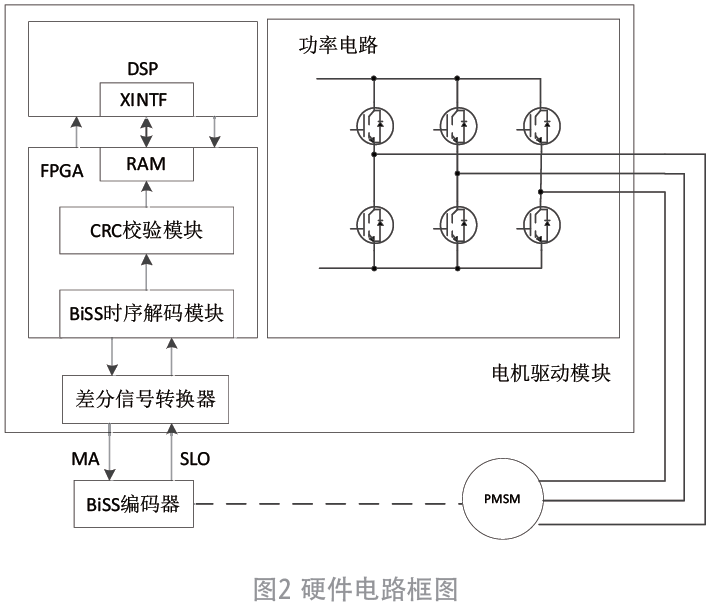

电机控制模块采用DSP+FPGA 双控制器方式,FPGA 负责采集与永磁同步电机同轴安装的BiSS 编码器位置数据,提供给DSP 用于FOC 算法计算。FPGA通过内部定时器定时执行BiSS 数据解码周期,每个周期内BiSS 时序解码模块产生BiSS 总线MA 时钟,直到该帧数据时序完成,同时接收BiSS 总线SLO 数据线数据,根据BiSS 时序定义从中提取出有用的位置、错误位、警告位、CRC 校验位数据段送至CRC 校验模块进行处理,根据BiSS 编码器的时序长度可以灵活调整定时器采样频率,以实现最大采样频率。CRC 校验模块按照协议规定的校验规则计算出收到有效数据位所对应的CRC 校验码,并与收到数据中的CRC 校验位段进行对比,若两者一致则判断该帧数据校验正确,为有效数据,并将经过校验的正确数据存入FPGA 内RAM 单元,DSP 通过XINTF 接口定时从FPGA 内部RAM 读取解析到的编码器位置数据,完成BiSS-B 协议编码器数据解码;若两者不一致则判断校验错误,将该帧数据丢弃,并对错误次数进行计数,连续数次检验到错误数据则发出报警信号触发DSP 启动保护措施,防止电机飞车。硬件电路框图如图2 所示。

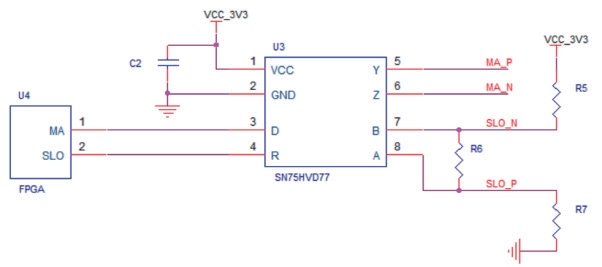

BiSS-B 协议编码器物理接口为RS422 电平标准,使用TI 公司的高速全双工RS485 收发器SN65HVD77将FPGA 的MA 时钟信号和SLO 数据信号将电平转换为两组差分信号线,连接至BiSS 协议编码器。该收发器支持信号传输速率>50 Mbit/s,可涵盖BiSS 协议最高传输速率。接口电路图如图3 所示。

图3 接口电路图

解码器软件设计

软件设计主要涉及通过FPGA 完成对BiSS-B 协议数据帧的解码以及对解码结果的校验,以下从状态机设计和CRC 校验器设计两方面进行介绍。文中编码器使用亨士乐公司的AD36-1213AF.0RBI 型多圈绝对式编码器。

2.1 状态机设计

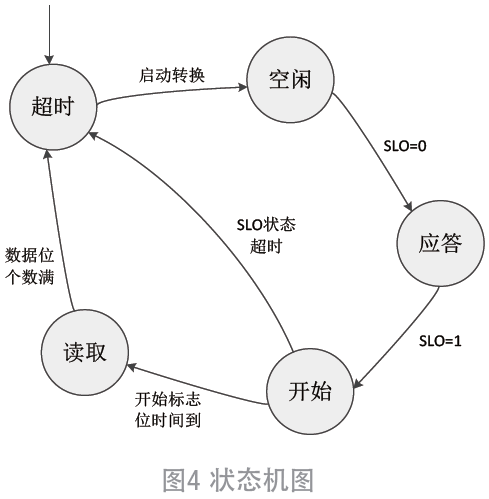

BiSS-B 协议时序具有数据帧长度不固定、数据帧信息复杂的特点,状态机是FPGA 设计中常用的一种设计方法,基于状态机的设计可大大提高设计的灵活性和通用性,因此文中设计了基于状态机的BiSS-B 协议时

序解码模块。根据图1 中BiSS-B 协议时序,FPGA 作为主设备,BiSS 编码器作为从设备,FPGA 解码模块初始状态为超时状态,应将时钟线MA 状态拉高,并确认数据线SLO 状态为常高。当超时状态准备就绪后,通过将时钟线MA 状态拉低1 个时钟启动1 次BiSS 协议编码器数据转换,并将状态机状态切换为空闲状态,等待数据线SLO 上从设备应答响应。正常情况下从设备将数据线SLO 状态拉低一段时间,状态机将转入应答状态。待从设备将数据线SLO 状态再次拉高时,状态机转入开始状态,并检测SLO 高状态时长,若时长为1 个MA 时钟则转入读取状态,否则将回到初始超时状态。在读取状态中,将对数据线SLO 上的数据进行读取,直到数据位数达到时序协议中规定的位数,然后将时钟线MA状态拉高转入超时状态,等待开始下一次循环。整个流程如图4 所示。

2.2 CRC校验模块设计

CRC 校验全称为循环冗余校验,是一种常用于检测通信协议或存储设备中原始数据是否发生数据位意外变动的错误检测算法[9]。其基本思想是对实际有用数据位按照一定的计算方法提取出对应的唯一一组特征值,将特征值附加在有用数据后发送至数据接收端,接收端将读取到的数据按照同样的计算方法得到一组特征值,若两组特征值一致则表示读取数据有效。

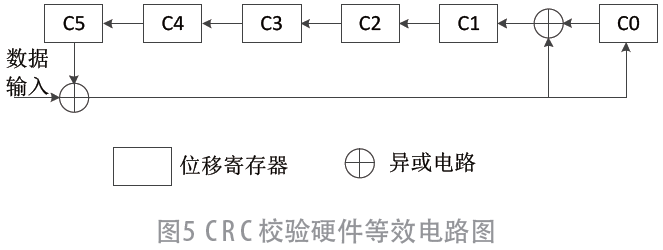

文中BiSS-B 协议编码器产品手册规定CRC 校验采用CRC-6 校验算法,其等效多项式为:

X6+X+1 (1)

可以利用一组移位寄存器和异或门电路来进行等效电路计算CRC-6 算法校验结果,其硬件等效电路如图5 所示,C5-C0 对应6 位移位寄存器从高至低的每位。

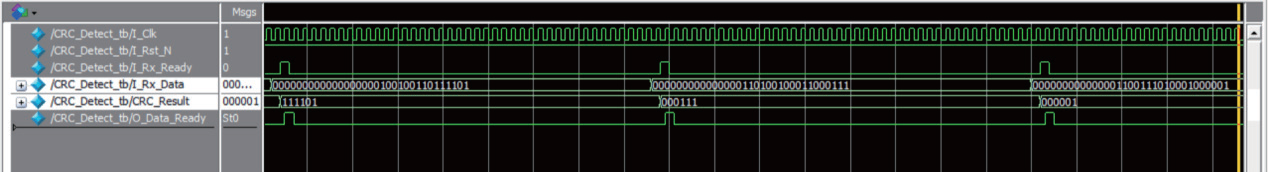

CRC 校验模块输入数据从最高位开始逐位与CRC校验结果字段最高位bit5 进行异或运算,异或结果作为CRC 校验结果字段的最低位bit0,并同时与bit0 异或,其结果作为bit1,其他bit 位依次为低1 bit 位移位结果。按照上述方式,应对AD36-1213AF.0RBI 型编码器的位置数据位、error 位、Warn 位和CRC 校验位进行CRC 校验,并将校验结果与CRC 校验位进行对比。使用Modelsim 对CRC 校验模块设计的合理性进行验证。验证结果如图6 所示。在图6 中,I_Rx_Data 为33 位经BiSS 时序解码模块提取的数据,CRC_Result 为CRC 校验结果,连续3组CRC 校验结果和对应的三组输入数据末6 位CRC 位一致,表明CRC 校验正确。

图6 Modelsim CRC校验结果图

3 实验验证

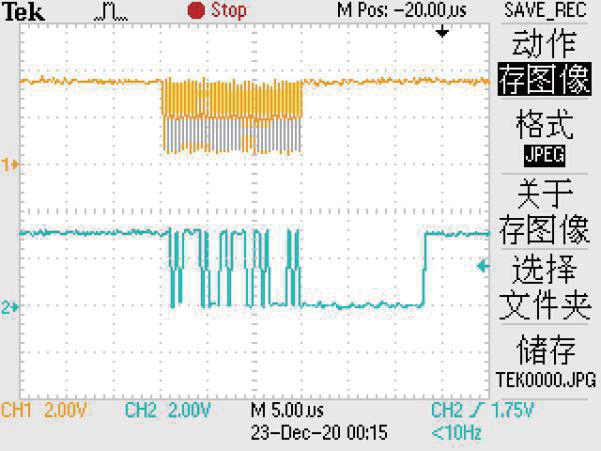

以EP4CE30 型FPGA 和TMS320F28335 型DSP 构成的硬件电路为基础,对BiSS-B 编码器数据进行了采集解析,图7 所示为FPGA 端BiSS-B 编码器数据时序监测结果,通道1 为MA 时钟线波形,频率为5 MHz,通道2 为SLO 数据线波形,由图中可见完成1 次数据解析时间约30 μs,可满足至少20 kHz 的编码器数据采样速率。

图7 BiSS-B编码器波形图

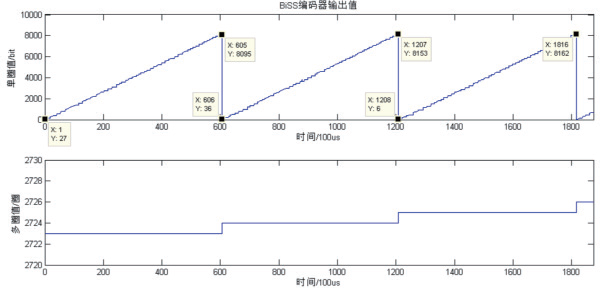

电机驱动模块速度环给定转速为1 000 r/m,连续采样多个周期的AD36-1213AF.0RBI 型编码器未经滤波处理的原始数据并解析出对应单圈和多圈位置数据,如图8 所示。

图8 BiSS-B编码器单圈/多圈数据图

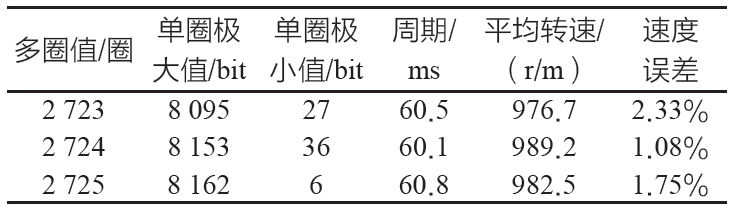

编码器单圈/ 多圈数据值分布情况如表1 为所示。依据多个连续周期里编码器数据计算出的平均转速与给定转速差异较小,可知编码器数据值采样正确,一致性较好。

表1 编码器单圈/多圈值

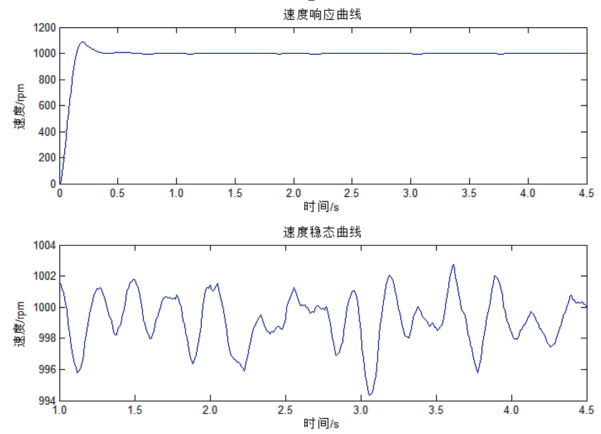

采集速度环反馈转速响应曲线,如图9 所示。由图中可见,使用BiSS 编码器作为位置传感器时电机速度环响应较快,超调量小于8%,稳态误差小于0.6%,具有较好的动态和稳态性能。验证了该BiSS 解码器设计的合理性。

图9 电机速度响应曲线图

4 结束语

通过对BiSS 协议的分析基础上,文中提出了BiSS协议编码器解码方案,通过实物试验验证了该方案的合理性,具有解析准确、采样速度快的特点,对不同的BiSS 协议具有适用性,适合应用于BiSS 协议编码器数据解析场合中。

参考文献:

[1] 王列虎,皮佑国.基于BISS协议的编码器接口技术研究及应用[J].机床与液压,2011,39(8):121.

[2] 王希远,成荣,朱煜,等.基于FPGA的BiSS-C协议编码器接口技术研究及解码实现[J].液晶与显示,2016,31(4):386.

[3] 孙彦超.基于XMC4500的PMSM控制系统的设计[D].沈阳:沈阳航空航天大学,2016.

[4] Texas Instruments Incorporated.TMS320F2837xD Dual-Core Defiino Microcontrollers Technical Reference Manual[R/OL].https://www.ti.com.cn/product/cn/TMS320F28379D?keyMatch=TMS320F2837&tisearch=Search-CNeverything.

[5] 商怀昊,韩基鹏,肖鹏,等.基于BiSS-C协议的编码器的接口技术研究及其在伺服驱动系统中的应用[J].工业技术创新,2014,1(2):211.

[6] 霍海龙.基于BiSS协议的编码器及其在伺服驱动系统中的应用[J].电气自动化,2011,33(3):12.

[7] HENGSTLER.Technical Manual SSI_BiSS_ACURO_en[R/OL].http://hengstler.com.cn/product/AD36.

[8] RENISHAW.biss_encoder_9709-9007-03-b(zh)[R/OL].https://www.renishaw.com.cn/zh/resolute-encoderseries--37823

[9] 朱正鹏,朱旭锋,李宾,等.一种位宽可变的CRC校验算法及硬件实现[J].航天控制,2019,37(2):42.

(本文来源于威廉希尔 官网app 杂志2021年8月期)

评论