毛军发院士:半导体异质集成电路的现状与挑战

1 背景与意义

本文引用地址://www.cazqn.com/article/202108/427609.htm芯片现在有2 条主要发展路线:①延续摩尔定律;②绕道摩尔定律。摩尔定律现在面临一些挑战,物理极限挑战;技术手段挑战;经济成本挑战——光算经济账都不得了。绕道摩尔定律有很多途径,途径之一是异质集成电路。

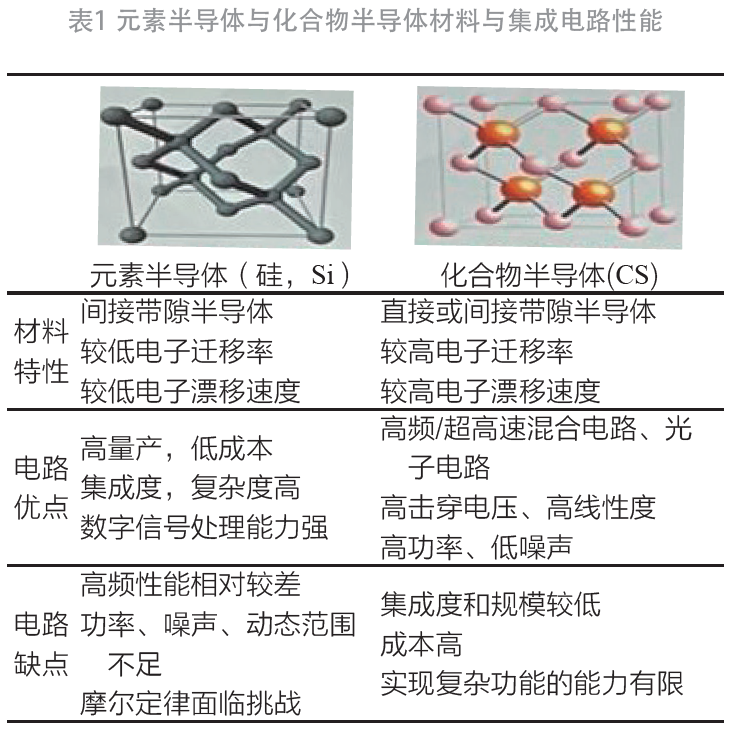

有2 类主要的半导体材料:①以硅为代表的元素半导体;②以砷化镓等为代表的化合物半导体。这两类半导体各有优缺点,从材料到电路优点很突出,电路缺点也很突出(表1)。

现状是一些复杂的电子系统,如毫米波收发前端系统,用任何单一的半导体工艺都较难完美实现(图2),有些部件用SiGe 芯片,有些部件更适合用GaN 芯片,所以人们自然而然地想到有没有一种办法把不同节点的半导体材料工艺结合起来。异质集成就具有这个功能。

半导体异质集成电路是将不同工艺节点的化合物半导体高性能器件或芯片、硅基低成本高集成器件组成芯片(都含光电子器件或芯片)与无源元件(含MEMS)或天线,通过异质键合或外延生长等方式集成而实现的集成电路或系统。

图1 中国科学院院士,上海交通大学党委常委、副校长毛军发

异质集成特色很突出:①可以融合不同的半导体材料、工艺、结构和元器件或芯片的优点;②采用系统设计理念;③应用先进技术,例如IP 和小芯片(chiplet),以及集成无源器件等新技术;具有2.5 维或3 维高密度结构。正因为这些特色,所以异质集成的优点很突出:①实现强大的复杂功能、优异的综合性能,突破单一半导体工艺的性能极限;②灵活性大,可靠性高,研发周期短,成本低;③ 3 维集成可以实现小型化、轻质化;④对半导体设备要求相对比较低,不受EUV 光刻机限制,因此是“超越摩尔定律”的重要路线之一。

1.2 毫米波异质集成电路

在半导体异质集成电路中有种特殊的集成电路:毫米波异质集成电路。毫米波是从(30 ~ 300)GHz 的波段,带宽很宽,而且器件小型化,所以也是国际上半导体异质集成电路发展的重点方向。

现在对异质集成电路需求迫切,主要有3 个原因:①从5G、6G 到航天导航、无人驾驶、智能装备、物联网等都需要毫米波技术;②毫米波系统包括数字电路、模拟电路、射频微波电路,所以对于异质集成的需求更加迫切;③毫米波异质所面临的挑战和问题更为严峻和复杂:因为频率高,具有分布式参数,从“路”向场演变,设计更加困难;波长短,模块之间的间距只有微米量级,集成度高,对工艺要求更加精细;有电磁寄生效应,耦合紧密,测试更加复杂。

研究半导体异质集成的科学意义也是很显著的。可以通过集成电路从目前单一同质工艺向多种异质工艺集成方向发展,从目前2 维平面集成向3 维立集成方向发展,从Top-Down(自顶向下)到Bottom-Up(自底向上)发展。

它的意义与价值是可以实现高性能的复杂系统。首先是电子系统集成技术发展的新途径;其次是后摩尔时代集成电路发展新方向;最后也是我国半导体集成电路变道超车发展的新机遇。

2 现状与问题

2.1 国际上EDA、工艺、封装的研究基础和进展国际上从EDA 工具到工艺,到封装有一些研究基础和进展。

● 从工具来看,NAGS 开发了当前异质集成最先进的工艺,这些工艺的功能包括版图设计、电路综合分析,而且是与业界的标准工艺兼容的。

● 从工艺来看,目前有4 种主流的半导体异质集成工艺。最先进也是难度最大的是异质外延生长工艺,它是器件级的异质集成;另外3 种包括异质外延转移、小芯片微米级组装、异质晶圆键合(是小系统级的集成),各有优缺点。

异质集成电路样品研究发展也有很多进展。例如美国DRAPA 的SMART 项目中,研制出44 GHz 的毫米波雷达系统,整个阵列厚度小于10 mm,功能密度相比传统提高了2 个数量级。

小芯片也有很多进展,不管是互联还是多种形式。例如英特尔和三星在2020 年IEDM 重要的半导体国际会议都发布了3 维异质集成的产品。台积电是以代工著称,但是近几年高度重视芯片的封装集成的技术,而且起点非常高,例如他们用最先进的3D Fabric 制作出3 维堆叠的芯片——SoIC,达到12 层,还有台积电用于智能手机的3D System。

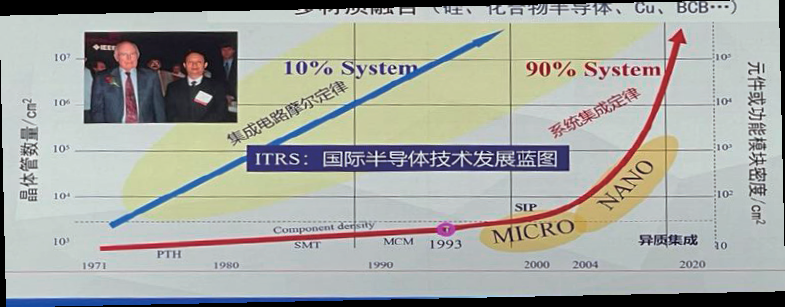

● 封装技术的重心正在慢慢从后端封装厂移到前端半导体代工厂。芯片有一个摩尔定律,封装集成有一个系统集成定律,指的是复杂电子系统中能够集成的芯片数量、元器件数量也是每18 个月或2 年翻一番,功能提高1 倍,成本下降一半。图3 是系统集成定律的曲线,可见更加陡峭。

图3 集成电路摩尔定律与系统集成定律

2.2 异质集成发展蓝图(HIR)带来的挑战

根据异质集成发展蓝图(HIR)[ 注:以前叫国际半导体发展蓝图(ITRS),现在已停止发布了],总体趋势也是集成度和工作速度不断提高,特别是电子、光电、机械一体化集成,这也是重要的发展趋势。这样就带来三大主要挑战:多物理调控(电磁、温度、应力);多性能协同(信号/ 电源完整性、热、力……);多材质融合(半导体硅、化合物半导体、Cu 等金属、BCB材料……)。

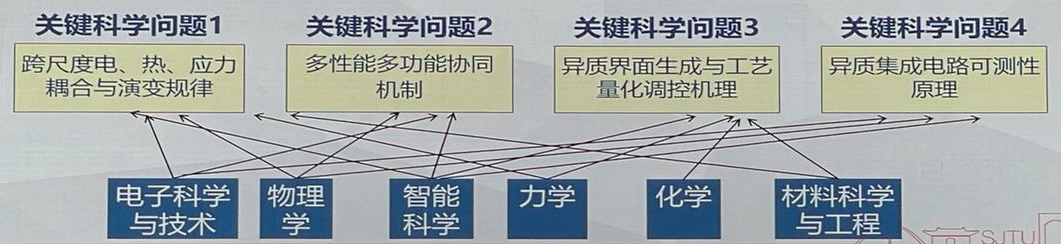

这三大挑战就会引起4 个主要科技问题:①跨尺度电、热、应力多物理场紧密耦合;②多性能、多功能协同机制、电特性、应力特性、热特性往往是相互矛盾的,功能也需要协同;③由于不同的材料晶格、膨胀系数差异,需建立异质界面动力学,认识扩散、成核、粘合机理,通过界面调控融合实现高可靠异质集成。异质集成受制于电、热、应力多物理特性,我们要认识它们之间的内在关系,从而实现半导体工艺量化设计与控制。目前的工艺主要是一些定性分析和量化,我们希望能够从定性走向定量,这也是一个飞跃。④异质集成电路可测性原理。因为是3 维高密度集成,探测点很少,耦合效应很严重,带来了测试挑战,因此我们要掌握可测性原理,建立物理特性可测试的充分和必要认知。

针对这4 个问题,毛军发院士等专家提出了总体研究思路:打破集成电路传统“路”的思路,以耦合多物理场理论为基础,场、路结合,进行多学科交叉,包括电子科学与技术、物理学,特别是人工智能对电路的设计,需要力学、化学、材料等多学科交叉开展研究(如图4)。

图4 总体研究思路

3 成果与展望

未来10 年研究目标,包括把光电子和电子集成在一起,这个难度更大,我们也希望能够突破异质生长工艺,让软件完全商业化。

摩尔定律正面临严峻挑战,这也是一个转折点,也是一个机遇。

(本文来源于威廉希尔 官网app

杂志2021年8月期)

评论