一种5G信号接收机的本振合成装置

5G 一直被称为是行业应用的5G,5G 有三大应用场景,分别是eMBB(增强型移动宽带)、URLLC(超高可靠低时延)、mMTC(海量机器类终端通信)。5G技术的发展离不开高性能5G 信号接收机和发射机的支持。随着5G 的不断演进和5G 垂直行业应用的不断深入,5G 相关指标和技术不断更新,这些变化都对5G 信号接收装置提出了新的要求,需要更大的带宽、更快的响应速度、更精确的解调精度等[1-3]。本文采用宽带VCO、鉴相器、分频器、预分频器等组成的锁相环方案,实现了一种可以覆盖3GPP R16 版本要求的5G FR1 频段的5G 接收机本振发生装置。

本文引用地址://www.cazqn.com/article/202106/426370.htm

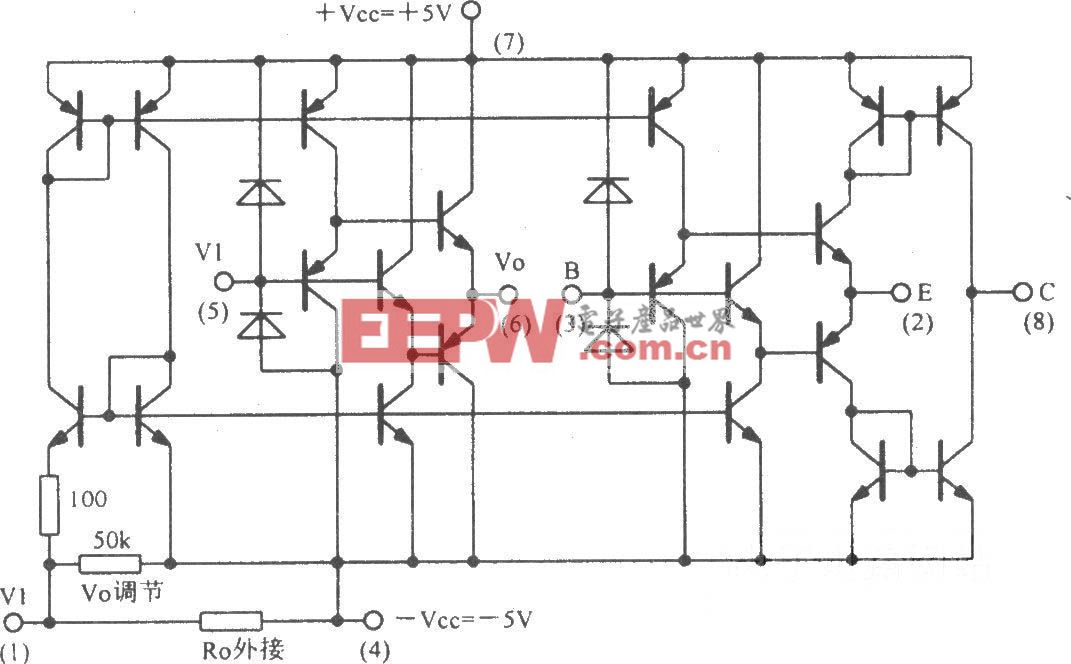

图1 HMC983的功能框图

1 方案设计

5G 信号接收机,一般由本振模块、接收通道模块、高速信号传输模块、数字信号分析模块、工控控制模块等部分组成,本文介绍了一种可以覆盖3GPP R16 版本规定5G FR1 频段(410~7 125)MHz 无线频率范围新要求的本振装置。

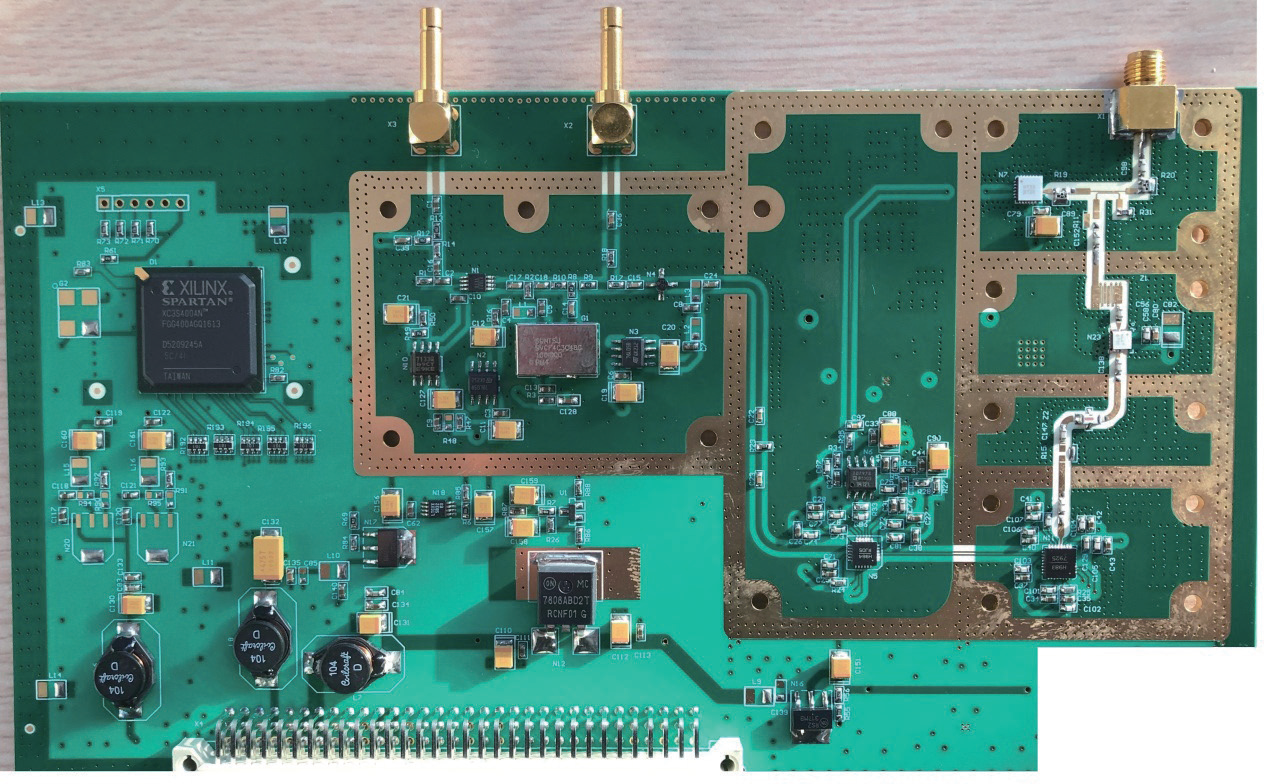

采用基于宽带高性能VCO(ADI 公司HMC773LC4B)的本振模块,输出(10~20)GHz 的本振信号是5G 信号分析仪整机射频电路的核心模块,其功能块包括:参考环电路、鉴相电路、Σ-Δ 调制、预分频电路、耦合反馈回路及FPGA 控制电路等。HMC983LP5E 功能框图如图1 所示,其工作频率为DC~7 GHz,因此需要在锁相环反馈回路中添加预置四分频器HMC447LC3,将频率变为(2.5~5)GHz。

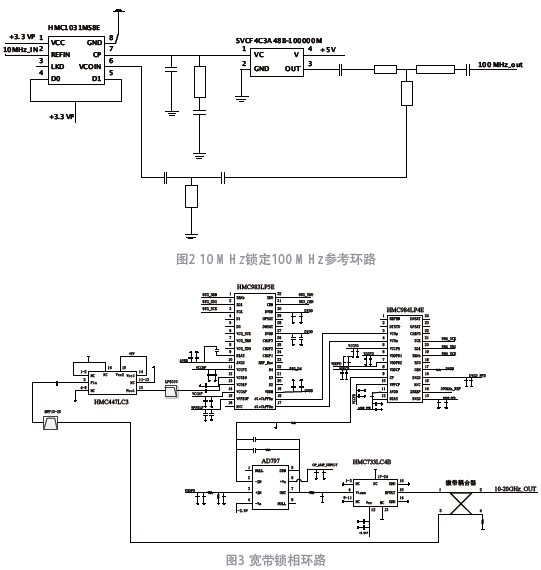

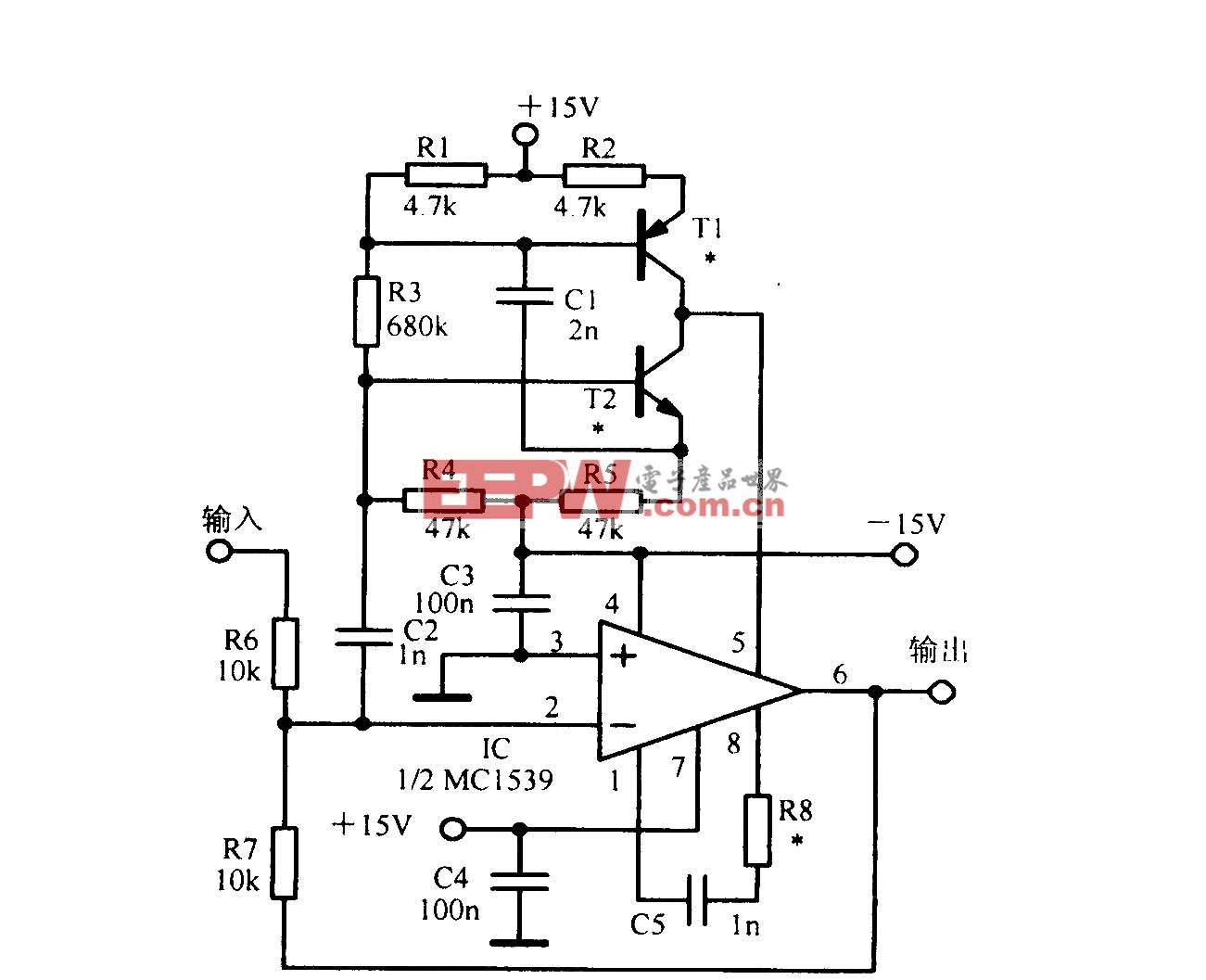

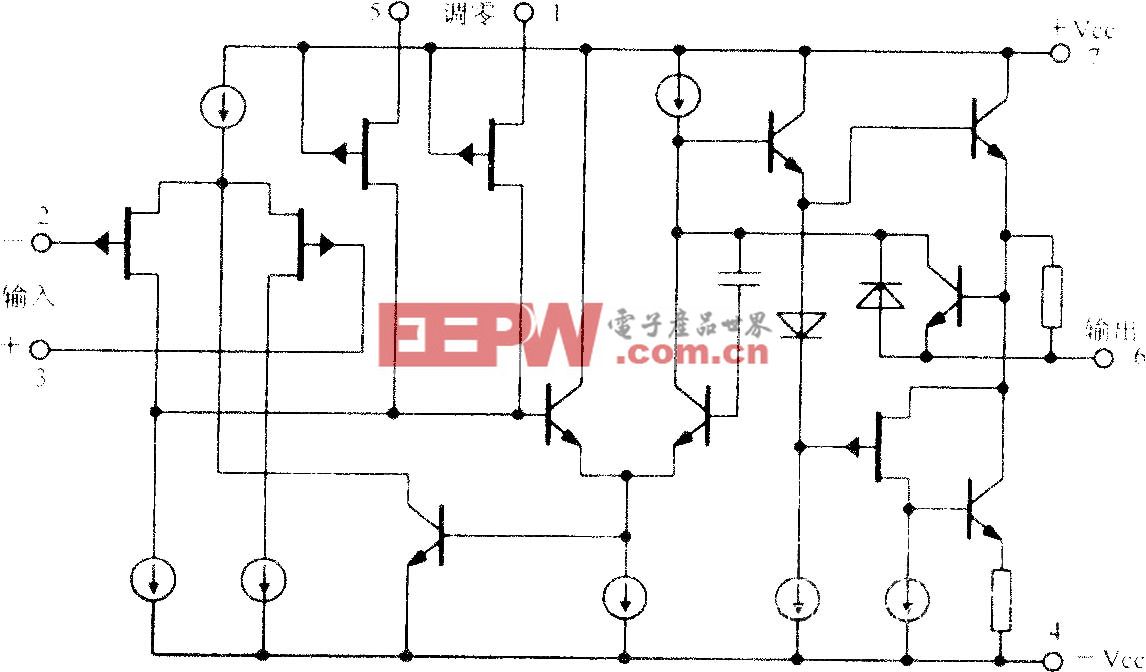

方案中的各个模块原理图及功能简介如下:图2 为100 MHz参考环路模块,通过HMC1031MS8E鉴相比较,实现10 MHz 锁定100 MHz 参考环路;图3 为宽带锁相环路模块,通过HMC983LP5E 分频器、HMC984LP4E鉴相器、有源环路滤波器、宽带耦合微带电路、预分频电路实现(10~20)GHz 的宽带锁相环路。

2 实验过程

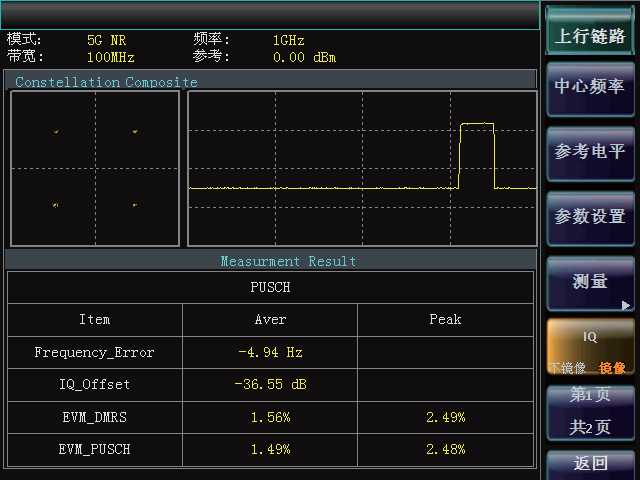

本文研制过程中的一种5G 信号接收机的本振合成装置的原理图和PCB 绘制使用的是Altium Design 工具。按照1 中的方案描述,使用Altium Design 工具绘制了对应原理图和PCB,使用SMT 将元器件焊接在板上,完成本振合成装置。接口方面,有为整机提供的10 MHz参考输入;100 MHz参考输出,为整机点频第二、第三本振提供参考;(10~20)GHz 本振输出,为接收通道混频模块提供激励本振源,完成频率变换;FPGA下载接口用于在线调试和bit 文件烧写;96 芯接插件为本振合成装置与整机母板之间的电源、数据线、地址线、控制线提供通路。图4 为完成的本振合成装置正面图片。红色部分为FPGA 控制模块的主要本振频率控制功能;蓝色部分为10 MHz 外部参考,锁定到100 MHz,用于(10~20)GHz 锁相环的参考和整机其他模块;黄色部分为本振合成装置的供电模块,为FPGA、VCO、放大器、开关、分频器、鉴相器等提供+5 V、+15 V、+30 V、-15 V 等电源;紫色部分为本振装置的核心模块,包括鉴相器、小数分频器、宽带耦合器、宽带压控振荡器、微带带通滤波器、预置4 分频器等,完成100 MHz 参考输入实现(10~20)GHz 宽带信号输出,为5G 信号接收机提供本振源。

图4 本振合成装置

3 测试结果

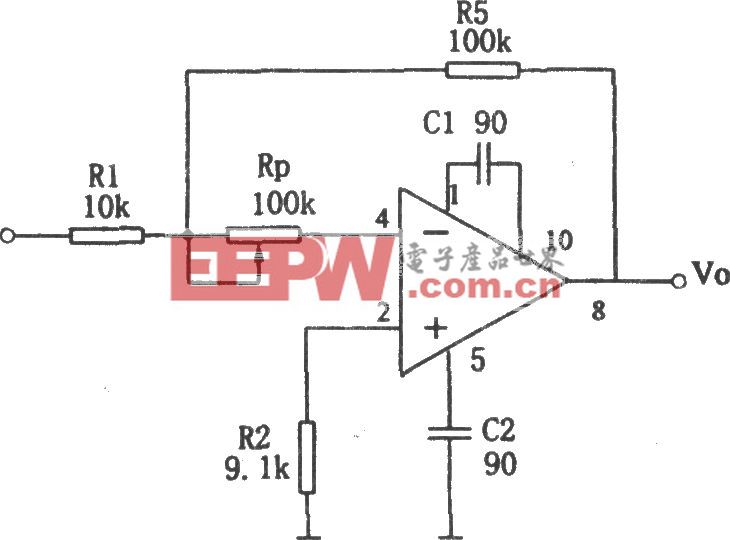

将本方案的本振合成装置接入有接收通道装置、频谱分析装置、宽带信号分析装置、键盘控制装置、工控接口装置、显示装置、二/ 三本振装置、时钟参考装置等的5G 信号接收机中,配合驱动程序、硬件控制程序、显示程序等组成完整的5G 信号接收机,通过对5G FR1 100 MHz 带宽的标准5G 信号分析能够呈现本振合成装置的性能。使用射频线缆连接矢量信号源与装入本振合成装置的5G 信号接收机,信号源发射1 GHz 中心频点的100 MHz 带宽上行PUSCH 信号,5G 信号接收机配置对应参数,解析界面如图5 所示。解调结果表明,EVM 均值为1.49%,频率误差为-4.94 Hz,IQ_offset 为-36.55 dB。

图5 100 MHz 5G PUSCH信号解调图

4 结束语

通过宽带VCO 的锁相环实现高频宽带、高性能的本振方案,可以满足5G 信号接收装置的需求,依照本方案设计的本振合成装置成功应用到了5G 信号接收机,正移植到5G 信号发生器中。

参考文献:

[1] 远坂俊昭.锁相环(PLL)电路设计与应用[M].何希才,译.北京:科学出版社,2006.

[2] 杜勇.锁相环技术原理及FPGA实现[M].北京:电子工业出版社,2016.

[3] 陈山枝,胡金玲,等.蜂窝车联网(C-V2X).[M].北京:人民邮电出版社,2020.

[4] Hittite Microwave Corporation.HMC984LP4E DIGITALPHASE-FREQUENCY DETECTOR[Z].Chelmsford:Hittite.

[5] Hittite Microwave Corporation.HMC983LP5E DC-7GHZ FRACTIONAL-N DIVIDER AND FREQUENCYSWEEPER[Z].Chelmsford:Hittite.

(本文来源于威廉希尔 官网app

杂志社2021年6月期)

评论