基于STM32F4和CPLD的高品质立体声USB数字音频接口设计

引言

在高品质音频回放系统中,USB协议[1]被广泛应用于音频数据的传输。目前高品质音频设备大多基于USB Audio Devices Class(以下简称ADC)2.0规范[2]开发USB音频接口。当前较为常见的USB音频接口方案的核心芯片有如下以下几种选择:1、专用USB音频接口芯片;2、XMOS系列芯片;3、带有USB2.0模块的通用单片机;4、FPGA芯片。从产品成本和生命周期考虑,产品方案中核心芯片应该选择市场上占有率大产品线成熟产品支持完善且价格相对低廉的型号。专用芯片底层不透明适用范围窄难以根据需求进行个性化开发,XMOS芯片产品支持较少开发文档不丰富,FPGA芯片开发难度和成本较高。通用单片机是一个较好的选择,但通用单片机的数字音频输出功能通常较薄弱需要对其进行一定的扩充。本文基于市场上应用广泛的STM32F4芯片和CPLD芯片设计了一款高性能USB数字音频接口。

本文所设计音频接口指标和特性如下:

1)支持的音频数据流格式:16bit PCM、32bit PCM、DoP(DSD Audio over PCM Frames)、NativeDSD;

2)支持的最高数据规格:384kHz PCM、DSD256;

3)输出接口规范:I2S、DSD;

4)异步反馈模式,主机时钟与设备时钟完全解耦,数字输出信号质量可控;

5)适配Windows、Linux系统原生ADC 2.0音频驱动。

1 基于ADC 2.0规范的立体声音频架构设计

ADC 2.0规范相较于其1.0版本架构更复杂包含的内容更为丰富,也增加了开发的难度。ADC 2.0物理层面上基于USB 2.0协议,完全支持高速USB传输,带宽不再受限。逻辑层面上,ADC 2.0规范为尽可能满足不同的音频数据传输需求,规定了一套较为复杂的抽象层逻辑。其中USB音频功能通过定义完善的接口来实现与外部的连通。每个音频功能都必须包含一个音频控制接口和可选的音频流接口。音频控制接口用于访问对应的音频功能,音频流接口用于传输音频数据。

为有效操地操作各种音频功能,ADC规范将其分割为不同的实体,依据功能特征实体可分为三大类:单元、端口、时钟。音频设备通过设备描述符定义音频控制接口、音频流接口和功能实体并将其从逻辑上串接在一起向主机描述设备所能实现的逻辑行为。

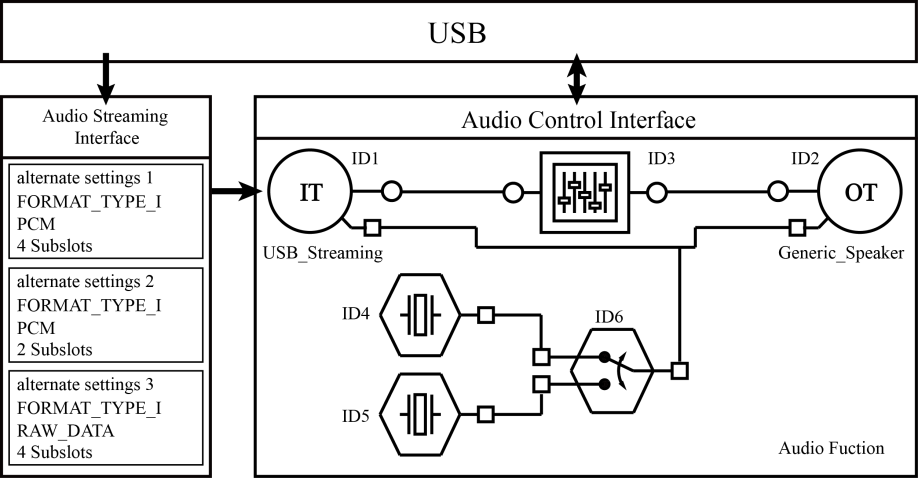

基于ADC2.0规范设计功能架构如图1所示。

1)Audio Streaming Interface定义了主机到设备的数据传输接口。该接口有3个备选接口设置分别用于传输32bit PCM、16bit PCM和NativeDSD数据。

2)Audio Control Interface定义了主机到设备的控制接口,该接口下包含了用于传输音频数据和实现部分功能的实体,主机通过设备请求来访问不同实体的具体功能。ID1是input terminal用于接收USB数据流也定义了输出声道的数量;ID2是output terminal相当于一个消耗USB数据的终端,主机一般需要结合audio streaming接口和端点描述符来确定此终端的具体特征行为;ID3是feature unit使能了音量控制和静音控制;ID4、ID5是clock source,用于描述时钟特征;ID6是clock selector,用于选择时钟信号的连接方式。

依据ADC规范编写设备的配置描述符即可定义此架构的逻辑结构,主机通过获取配置描述符来知晓设备所具有的接口和功能。需要注意的是ADC仅仅提供了一个完整的协议框架,本身并不实现任何具体功能,开发者遵循ADC规范开发设备和驱动可提高产品和驱动的通用性。

图1 基于ADC 2.0规范的音频接口逻辑架构

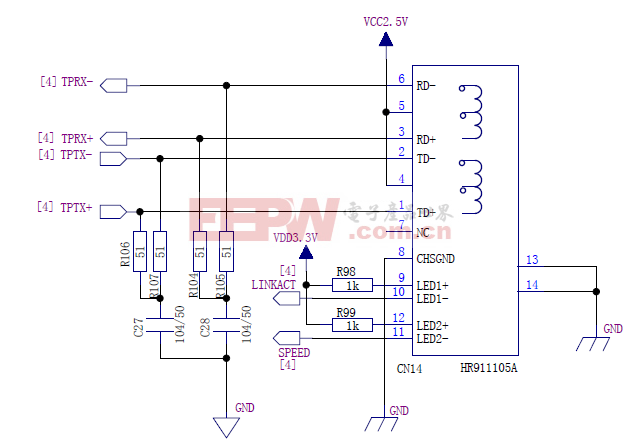

2 基于STM32F4 的USB Audio Class设备设计

由于ADC2.0规范是基于USB2.0协议的[2],需要设备具有高速传输能力。STM32F4的高速USB OTG模块没有片上高速PHY,只有UPLI接口,因此需要外接USB UPLI芯片来实现高速USB功能。本设计采用了较为常用的USB3300芯片与STM32F4连接,STM32F4提供完整的UPLI协议硬件支持[3],只需要操作对应的寄存器即可实现相应的通信功能,不需要过多关注USB控制器具体底层的操作,大大降低了程序设计难度。

2.1 音频数据传输和频率反馈控制

依据ADC规范,设备需要使用等时端点来传输音频数据。由于主机和设备的时钟存在频率误差、相位误差和相位抖动,为保证音频数据传输的完整连贯性,必须在主机和设备间建立一种同步机制。USB协议针对等时传输提供了三种同步方案[1],以设备角度来分析如下

1)将设备时钟同步到主机SOF(帧起始)信号上;

2)设备根据主机发送数据的速率调整数据消耗速率;

3)设备和主机独立运行在自己的时钟上,设备提供时钟速度的显式反馈。

方案1)音频回放质量依赖于主机时钟质量和频率跟踪误差,方案2)设备为保持同步必须在软件里动态调节回放频率直接造成失真。只有方案3)才能完全消除主机和设备间的时钟耦合,这是高品质回放的必要条件。

在一般音频驱动程序中,主机使用EP1 OUT端点来传输音频数据,使用EP1 IN端点来进行传输频率的反馈。当播放开始后,主机每个微帧都会向EP1发送音频数据,主机每4微帧向EP1请求一次4字节的IN传输。IN传输返回的数据是一个频率参数,主机根据此参数动态地调整每个微帧发送的数据帧数量从而调节数据发送速率。

由于主机和设备独立运行在各自的时钟源上,因此主机发送数据频率和设备消耗数据频率不可能完全一致,如果不进行处理会出现数据溢出和丢失问题。解决方案是在设备程序中设计一个缓冲区暂存数据,根据缓冲区长度向主机发送需要的数据速率来进行滞环控制,从而实现对缓冲区数据长度的跟踪。环宽和跟踪目标的选择需结合主机和设备时钟的最大可能误差以及控制芯片允许的存储空间来确定。依据USB 2.0协议,高速传输的比特率精度应控制在500ppm(0.05%)以内,设环宽为,数据速率为则。

因主机传输数据以微帧为单位,设每个微帧内可能传输的最大数据量为字节,为防止数据上溢或下溢,追踪数据长度应大于。

2.2 音频输出接口与STM32F4间的通信实现

由于STM32F4芯片自身音频接口功能有限,且不能直接输出DSD信号,所以只能考虑驳接外部芯片来实现设计目标。这部分功能主要是完成音频信号时序输出,因此选用CPLD芯片较为合理。

从主机接收的USB音频数据在STM32F4芯片中处理后输出到CPLD芯片,二者之间需要一个传输的通道。本设计最高数据规格是PCM 32bit/384kHz,计算可得数据带宽为24.576Mbit/s,由参考手册[3]可知SPI1通道与高速USB接口复用无法使用其SPI功能,而其它SPI通道最高速率为21Mbit/s无法满足设计要求。因此需用并行传输来提高接口带宽,由于音频数据量大且对实时性要求很高,不宜直接通过操作IO口来输出数据,考虑使用STM32的DMA功能来实现并行传输。

得益于STM32F4的DMA IP核基于多层总线矩阵的设计,可以利用DMA和GPIO端口进行并行同步传输,其本质原理是利用某种触发机制实现数据从SRAM到GPIO的DMA传输[4]。

1)DMA控制器选择

STM32F4片上集成2个DMA IP。每个DMA各有一个存储器端口和一个外设端口。利用外部总线矩阵和专用DMA路径,不仅在DMA级两个端口可以同时工作,还可以实现DMA和系统其它主设备同时工作。GPIO位于AHB1总线上,由参考手册[3]可知STM32F4的DMA1的AHB外设端口没有连接到总线矩阵,因此只有DMA2可实现从SRAM到AHB1外设的访问。

2)触发机制选择

同步传输根据同步信号的提供者可将设备分为主从两方。本文以STM32F4作为从设备,CLPD作为主设备进行设计。CLPD向STM32发出同步信号来请求数据,当STM32接收到一个合法的触发信号应触发一次DMA传输,将存储器(源地址)上的数据由DMA控制器传输到GPIO(目标地址)上。这里就需要一个外设来接收并处理外部触发信号并产生DMA请求,显然定时器模块很适合完成这项工作。

由参考手册[3]可知只有两个高级控制定时器TIM1和TIM8可以产生DMA2的请求,但可产生DMA请求的事件比较丰富,本设计选择了TRIG事件来触发DMA请求。具体实现方法是将定时器设置为外部时钟触发模式,选择一个GPIO端口x的上升沿触发TRIG事件,每当CPLD在端口x处产生一个上升沿信号即触发DMA传输请求,数据从预设的地址传输到GPIO端口上,CPLD即可从相应端口并行地读入取此数据。

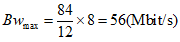

3)最大传输带宽计算

此设计中影响STM32F4到CPLD传输带宽的因素主要有DMA传输时间、定时器收入捕获数字滤波时间和CPLD端口建立时间。由于CPLD端口建立时间较短,此处不予考虑。

本设计DMA设置是从存储器传输数据到AHB外设,使用突发传输,不需要进行总线仲裁,则DMA数据流的总传输时间为:

TS=TSP+TSM

其中是DMA外设端口访问和传输的总时间,TSM是DMA存储器端口访问和传输的总时间。依据参考文献[5]计算可得,最坏情况下DMA传输时间为8个AHB周期。

定时器输入捕获数字滤波器是为了消除干扰引起的误触发,数字滤波器由事件计数器组成,每N个事件才视为一个有效边沿,将其设置为连续4个AHB周期。则从CPLD给出上升沿触发信号到CPLD读取到数据的延时为12个AHB周期。将AHB频率设置为84MHz,在用8位GPIO口并行输出的情况下,接口带宽为:

可见传输带宽完全满足设计需要。若使用整组16位GPIO做输出可降低芯片主时钟频率且为带宽留出较大裕度,为设备功能升级留有裕量。

2.3 音频信号的输出

本设计中,PCM音频信号输出采用I2S接口,DSD音频信号输出由DSD时钟信号和DSD左右声道数据信号构成[6]。

对于PCM数据,主机传入设备的数据是低字节在前高字节在后,而I2S协议是从数据高字节开始串行输出的;对于DSD数据而言主机整帧的传入数据而在信号输出端左右声道却是同时输出的。因此设备需要对原始数据进行重新组合处理。CPLD门资源较为有限,为降低片上资源的使用率和综合布线难度,处理数据的工作全部由STM32芯片负责。CPLD依据前述设计方案从STM32缓冲区依次并行读取数据再将数据按各播放模式的时序逻辑串行输出即可。

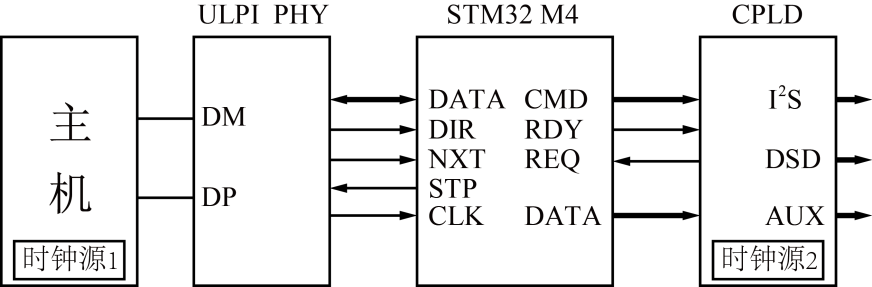

2.4 硬件连接框图

设备的主要硬件连接框图如图2所示。STM32通过ULPI PHY芯片与主机通信,与CPLD相连接的信号中CMD为控制信号,本设计使用SPI总线向CPLD发送控制指令。RDY为程序通知CLPD可以进行数据请求的信号。REQ为CPLD向STM32发送的数据请求信号,此信号即用于触发DMA请求。DATA为并行的数据信号。CPLD向外输出I2S和DSD时序信号,外部控制芯片可通过AUX接口来读取设备的相关状态。

主机时钟源1和负责提供回放时钟的时钟源2相互独立,因此时钟源2可以选用低相位噪声的时钟来提升音频回放质量。

图2 硬件连接框图

3 应用程序框架

由于基于上述设计方案的软件实现方案非常灵活,部分技术虽为通用技术但细节又较为繁琐,本节仅对一种可行性方案概括性说明。

此方案主要由三个模块构成:USB底层通信程序、Setup传输处理程序、播放处理程序。具体功能使用了三个状态机实现,由于USB通信程序中包含了硬件中断,三个状态机之间的通信由消息队列来实现异步通信。此处不对USB底层通信和Setup传输处理程序进行赘述,重点对播放处理的状态机设计进行说明。

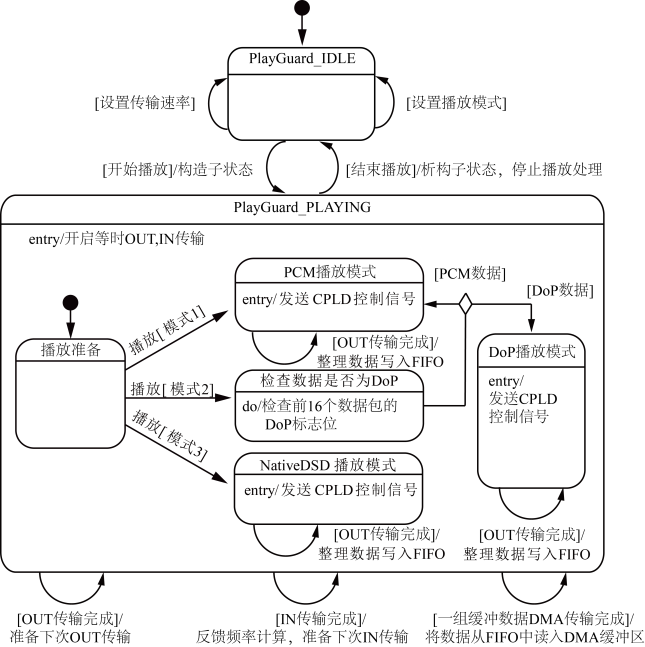

基于上述原理设计的播放处理状态机的UML状态图如图3所示,整个播放过程在播放监控状态中运行,在PlayGuard_IDLE状态中程序接收相关的参数设置信号为播放做准备。PlayGuard_PLAYING是一个组合状态,其自身负责与USB底层模块通信进行数据传输,其子状态负责处理特定播放模式。

音频数据的流转是程序的核心算法。音频数据通过OUT传输写入程序缓冲区,数据由播放子状态处理并写入FIFO中。程序将DMA传输设置为双缓冲模式,在DMA完成事件中从FIFO读出一组数据对双缓冲区进行交替填充。在IN传输完成事件中计算当前FIFO区数据长度据此反馈数据传输率给主机完成对数据长度的追踪控制。

图3 播放处理状态图

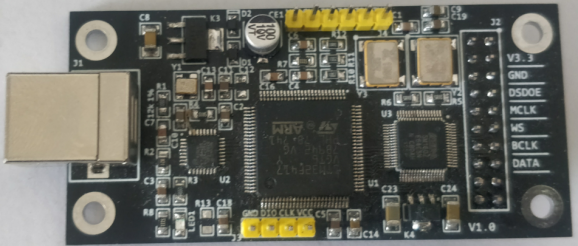

4 结语

基于上述设计制作了硬件实物如图4,分别在Windows 10系统和Linux发行版下进行测试实验,接口板在系统原生驱动下工作正常,可播放所支持规格的PCM音频文件。在三方驱动下可正常通过DoP模式或NativeDSD模式播放DSD音频文件。播放自定义音频文件并用逻辑分析采集输出接口的数据与源文件对比,接口板完整无失真的还原了源文件的数据。在软件开发平台上对缓冲队列进行监控,程序能较好的跟踪队列长度的稳定,无数据溢出现象。最后将接口板连接至解码器上进行试听,主观听感良好。以上试验证明设计达到了预期指标。

图4 硬件实物图

设计在以下方面还有进一步研究改进的空间:1、优化播放时钟设计,进一步降低回放失真;2、增加对更多声道音频格式的支持;3、增加数字音效的功能;4、增加Bootloader程序,实现主机对设备功能和参数的在线升级与修改。

参考文献:

[1] Universal Serial Bus Specification[EB/OL]. Revision 2.0, USB-IF,(2000-4-27)[2020-4-25].https://www.usb.org.

[2] Universal Serial Bus Device Class Definition for Audio Devices[EB/OL]. Release 2.0,USB-IF, (2006-5-31)[2020-4-25].https://www.usb.org.

[3] STM32F405/415, STM32F407/417, STM32F427/437 and STM32F429/439 advanced Arm®-based 32-bit MCUs Reference manual (RM0090)[EB/OL]. Rev 18, STMicroelectronics, (2019)[2020-4-25].https://www.st.com.

[4] Parallel synchronous transmission using GPIO and DMA(AN4666)[EB/OL]. Rev 1, STMicroelectronics, (2016)[2020-4-25].https://www.st.com.

[5] Using the STM32F2, STM32F4 and STM32F7 Series DMA controller(AN4031)[EB/OL]. Rev 3, STMicroelectronics, (2016)[2020-4-25].https://www.st.com.

[6] J. ROBERT STUART. Coding for High-Resolution Audio Systems[J]. Audio Eng. Soc., 2004,Vol. 52, No. 3:117-144.

(本文来源于威廉希尔 官网app 杂志2020年10月期)

评论