格罗方德12LP+ FinFET解决方案针对AI进行优化

格罗方德的差异化「12LP+」解决方案主要针对AI训练以及推论应用进行优化。本解决方案建立于验证过的平台上,具有强大的制造生态系统,可为芯片设计师带来高效能的开发体验,及快速的上市时间。

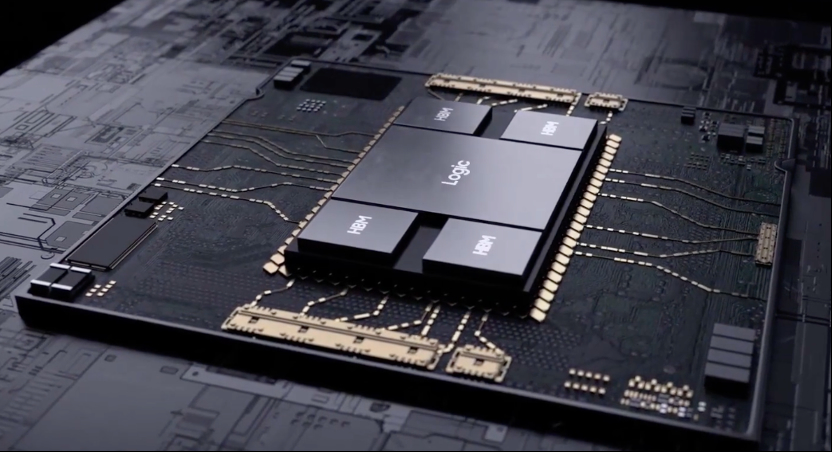

为达到性能、功耗和面积的组合,12LP+导入了若干新功能,包含更新后的标准组件库、用于2.5D封装的中介板,与一个低功耗的0.5V Vmin SRAM记忆单元,以支持AI处理器与内存之间的低延迟和低功耗数据往复,得致专为符合快速增长之AI市场的特定需所制定的半导体解决方案。

格罗方德资深副总裁兼运算暨有线基础架构部总经理Amir Faintuch表示:「AI循着脉络已会成为我们有生之年最具颠覆性的技术。越发明显的是,AI系统的效能 – 特别是能运用一瓦的功率执行多少次运作 – 成为企业决定投资数据中心或顶尖AI应用的关键因素之一。我们的全新12LP+解决方案能够直接处理这项挑战,而AI正是本解决方案在进行设计以及优化时,不变的初衷。」

12LP+建立在格罗方德14nm/12LP平台基础上,早已出货超过100万个晶圆。许多公司包含Enflame和Tenstorrent等,都将格罗方德的12LP用于AI加速器相关应用。藉由与AI客户紧密合作并互相学习,格罗方德开发出12LP+解决方案,为AI产业中的设计师提供更大的差异性以及更高的价值,并将开发及生产成本降至最低。12LP+性能得以增强的特点包括:与12LP相比,将SoC级的逻辑性能提高20%,而在逻辑芯片尺寸方面则缩小10%。这些进阶功能是透过12LP+的新一代标准组件库加以达成,其中包含性能驱动的面积优化组件、单一Fin单元、新的低压SRAM记忆单元以及改良版模拟布局设计规则。

格罗方德的AI设计参考套件及其协同开发、封装和晶圆生产后续统包服务,增强了格罗方德12LP+专业应用解决方案的能力。在设计低功耗、经济实惠且针对AI应用进行优化的电路时,更共同提供绝佳的整体体验。格罗方德与生态系统伙伴间的紧密合作,亦造就了符合成本效益的开发费用,并缩短了上市时间。

除了12LP现有的IP产品组合之外,格罗方德亦将扩展12LP+的验证范围,藉此将PCIe 3/4/5和USB 2/3并进主机处理器。此外,也将HBM2/2e、DDR/LPDDR4/4x和GDDR6纳入外部内存和芯片间互连技术,使设计师和客户往小芯片架构发展。

格罗方德的12LP+解决方案已通过技术验证,目前已准备在纽约州马耳他的Fab 8进行生产,预计在2020下半年进行试产。格罗方德先前已宣布,将使Fab 8符合美国国际武器贸易条例(ITAR)标准和出口管制条例(EAR)于今年底生效的管制措施,透过这项举措为Fab 8所生产的国防相关应用、装置或组件提供机密性和完整保护。

评论