面向5G且完全集成参考时钟的抖动衰减器 简化高速网络时钟设计

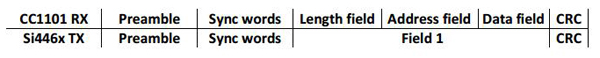

中国,北京 - 2019年6月20日 - Silicon Labs (亦称“芯科科技”,NASDAQ:SLAB)日前扩展了Si539x抖动衰减器系列产品,其新器件型号具有完全集成的参考时钟、增强了系统可靠性和性能,同时简化了高速网络设计中的PCB布局布线。新型Si539x抖动衰减器设计旨在满足100/200/400/600/800G设计中苛刻的参考时钟要求,为最先进的以太网交换机SoC、PHY、FPGA和ASIC中56G PAM-4 SerDes所需的严格抖动要求提供超过40%的余量,同时也为新兴的112G SerDes设计提供符合未来需求的解决方案。

本文引用地址://www.cazqn.com/article/201907/402292.htmSilicon Labs时钟产品总经理James Wilson表示: “网络设备供应商正在竞相开发能够处理5G无线流量的更高速、更高容量的设备。这种转变推动了对前传/回传(fronthaul/backhaul)、城域/核心以及数据中心应用中对更高性能时钟解决方案的需求。集成56 Gbps SerDes的FPGA和PHY支持更高容量的100/200/400/600/800G光纤和以太网线卡,但是却要面临越来越复杂的电路板设计以及布局布线带来的挑战。通过在Silicon Labs最新的Si539x抖动衰减器中集成参考时钟,助力整个行业更加轻松的迁移到更高端口数量、更高容量的100/200/400/600/800G设计。”

提高系统可靠性和性能 — 新型Si539x抖动衰减器集成了一个高度可靠的晶体,该晶体已在全温度范围内进行了全面测试,并针对活性下降(activity dip)进行了预筛选。 Si539x器件已经完全通过各种可靠性测试,包括冲击、振动、温度循环和晶体老化。规格严谨的晶体和创新的器件结构降低了晶体对系统风扇引起的温度变化的敏感度,从而实现更加一致、可靠的操作。

高声频发射噪声抗扰度 — 集成参考时钟的器件结构比外部晶体设计具有更高的声频发射(AE)抗扰度。AE是当PCB板经受温度梯度或外部机械力而导致PCB组装中的微裂纹或塑性变形时发生的噪声波辐射。与由于AE引起的更大频率误差的分立晶体不同,Si539x器件的创新封装结构可隔离并保护晶体免受AE噪声影响,确保可靠的操作和一致的频率响应。

节省板面积 — 设计高端口数的光纤和以太网线卡的客户非常重视缩减整体电路板面积。通过使用带有集成参考时钟的抖动衰减器,开发人员可以将PCB占位面积减少35%以上,并带来额外的益处:集成的参考时钟消除了对晶体下方的禁布区的需求,因此可在器件周围进行更密集的时钟布线,从而进一步简化了PCB布局布线。

频率灵活性和时钟分发 — Si539x器件可在多达12个差分时钟输出上产生100 Hz至1028 MHz频率的任意组合,无须常用的独立时钟发生器和时钟缓冲器。这些优势实现了“片上时钟树”时钟,同时消除了与离散时钟树解决方案相关的附加抖动。

价格与供货

新型Si539x抖动衰减器现已量产,可提供样片。 Silicon Labs提供各种评估板(EVB),零售价为299美元,它们适用于选择带有内部或外部参考时钟的Si539x器件。EVB使客户能够快速从设备配置转向详细的性能评估,通过与ClockBuilder Pro软件工具无缝协作,开发人员能够快速开发自定义配置并衡量性能。有关Si539x产品定价,请联系各地的Silicon Labs销售代表或授权经销商。

评论