基于CPLD的字符叠加器的设计

系统组成及基本原理

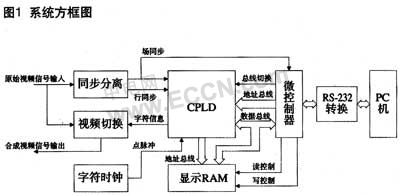

这种字符叠加器的系统方框图如图1所示。图中CPLD采用ispLSI1016,完成地址生成、总线切换、并串转换、地址锁存等核心功能。外围器件还包括微控制器、显示缓存RAM、以及RS-232串口电平转换芯片等。

CPLD内部电路主要由定时、并串转换、地址总线切换以及地址锁存等组成。

定时部分

该部分由八分频器、行计数器、列计数器以及消隐处理单元组成。

由于CPLD器件内部未内置时钟振荡器,所以其主振信号采用外部已经整形的脉冲信号。此设计中采用了带驱动的方形石英振荡器。通过计算,点时钟脉冲应该为8MHz左右。

将外部产生的时钟脉冲作为最高点脉冲。由于RAM的数据总线宽度是8位,这里将点脉冲进行8分频,得到字符脉冲,完成此功能的是一个3位同步计数器。然后再对字符时钟进行6位二进制计数,即列计数,由此可以知道一行横向最多可以显示64个英文字母或者32个汉字(受到CPLD容量和显示RAM空间的限制),完成此功能的是一个6位同步计数器。以上两个计数器的清零端接外部的行同步脉冲的反相信号。当行同步信号到来的时候,扫描进入回扫期,这时两个计数器都清零并不再计数,直到行同步信号消失。6位同步计数器计满需要52μs,正好与我国电视标准扫描正程时间相等。对其用外部行同步信号清零,则可以保证产生的字符信号与外部视频信号保持同步。此外,再用一个9位同步计数器来完成对行同步脉冲的计数,并用视频信号的场同步脉冲反相信号对其清零,该行同步计数器取值应小于312。最后,将行计数器和列计数器的输出依次接在显示RAM地址线上,建立起扫描时刻和显示RAM单元的联系,即显示RAM成了屏幕显示的映象。当扫描线扫到某固定位置,同时读出显示RAM相应单元的数据,这样就可以在屏幕上任意位置显示字符。

并串转换部分

该部分由并串转换单元和字符输出单元组成。

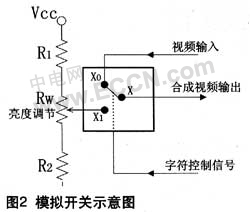

因为显示RAM的数据宽度是并行8位,所以为了视频叠加需要把它转换成串行的视频数据流,即需要一个并串转换电路。本文电路由一个带置数端的8位移位寄存器构成。当8分频的字符时钟到来时,将数据总线上显示RAM送出的8位字符数据存入寄存器,随后用点脉冲将数据逐一移出。为了保证在扫描回程中没有视频信号出现,字符输出单元将串行的视频数据流和行同步、场同步以及地址切换信号相与后再输出字符信息。 地址总线切换部分

由于并串转换部分需要不断从显示RAM中读取数据,以便转换成相应的视频数据流,同时微控制器也需通过随时修改显示RAM中的内容以达到改变屏幕显示的目的,显示RAM需要能够处理两条总线上的内容。为了使只有一条数据地址总线的普通RAM能够处理两条总线上的数据,需要有地址信号切换电路,这里选用双16位数据选择器。为了屏幕显示不受总线切换的影响,则要求总线切换必须在扫描逆程进行。 地址锁存部分

由于MCS-51系列的微控制器总线是数据地址复用的,而本设计中的微控制器采用的又是总线控制方式,所以地址和数据信号需要采用锁存器进行分离。在本设计中,将锁存器也置入CPLD内部,从而使外部的电路变得更简单。

对于该CPLD芯片的逻辑设计一般可采用硬件描述语言VerilogHDL或VHDL来完成,亦可采用如本设计中的原理图输入法来完成。

微控制器程序的设计

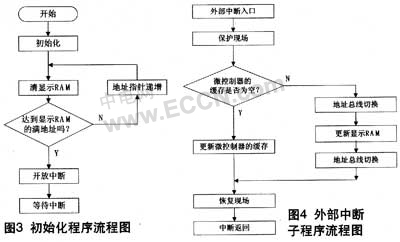

初始化程序主要用于系统的初始化配置、开放外中断及对显示RAM的清除,其流程及外部中断子程序流程图如图3、图4所示。

评论