基于FPGA的ARM图像缩放器的实现

ARM是目前全球最大的嵌入式芯片技术的IP提供商,其所拥有的IP已经成为众多芯片设计公司采纳的一种技术标准和开发平台。所以基于ARM 内核的SoC已经成为嵌入式处理器的开发重点,可通过ARM实现LCD控制器来完成对嵌入式LCD屏的控制。如果利用TFT屏支持显示,其图像分辨率存在局限性,因此通过搭建一个FPGA平台实现图像缩放器功能外接LCD显示器,完成ARM信号的扩展显示。同时FPGA也能完成对ARM平台产生的图像信号进行验证和仿真,以测试其功能和时序的正确性。XGA显示器因其显示量大,输出形式多样等特点已经成为目前大多数设计中的常用输出设备,因此本文针对ARM产生的VGA信号通过插值算法对其扩展为XGA标准信号。

本文引用地址://www.cazqn.com/article/189620.htm1 VESA标准中的VGA与XGA时序

视频电子标准协会(VESA)是非盈利国际组织,主要制定个人电脑、工作站以及消费电子类产品在视频接口标准,因此本文所设计的VGA与XGA的时序均按照VESA标准设计。

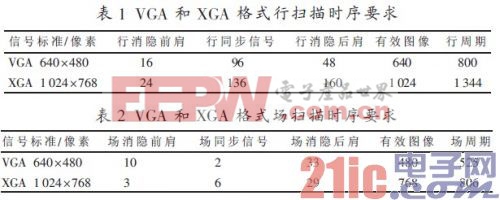

显示器通常采用逐行扫描的方式,每一帧图像按顺序一行接着一行连续扫描而成,扫描的过程中由水平同步信号HSYNC和垂直同步信号VSYNC来控制扫描。行扫描和场扫描的时序图如图1所示,其行扫描和场扫描的时序要求如表1、表2所示。

图1 行扫描时序和场扫描时序

2 系统整体设计

2.1系统框图

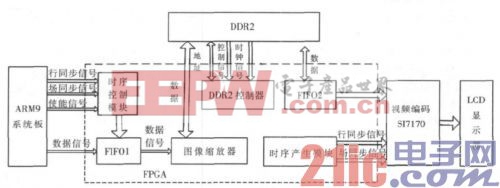

系统设计的数据源是来自ARM9系统板的视频信号,其格式为VESA标准的VGA信号。数据源进入FPGA后先进行图像缩放的处理,把输入的有效像素数据利用算法对其进行处理,期间的处理数据利用FIFO与DDR2进行缓存,然后把处理后的图像数据按照XGA时序送入视频编码芯片,最后送入显示器显示。其中FPGA内部设计分为时序控制模块、时序产生模块、FIFO模块、图像缩放器模块以及DDR2 SDRAM控制器模块,如图2所示。

图2 系统原理框图

2.2 硬件实现

FPGA采用Altera的EP3C16F484C6芯片,该芯片具有15 408个逻辑单元,504 KB内存,56个乘法器和4个PLL锁相环内核,最大支持346个I/O端口,系统时钟最高为250 MHz。FPGA开发板采用了专门的视频解码编码芯片,Silicon Image的视频编码芯片SI7170支持VGA到UVGA的格式标准,同时也支持HDTV格式的编码。DDR2 SDRAM采用三星的K4T51163QC芯片, 其频率支持267 MHz,本文选取为200 MHz。芯片容量为32 MB×16,实际上只要SDRAM满足存储2帧图像的容量即可满足本文设计要求[1]。完成转换后的XGA信号所需的输出时钟为65 MHz,可由FPGA内部锁相环产生。

fpga相关文章:fpga是什么

锁相环相关文章:锁相环原理

评论