MSP430系列MCU的动态时钟配置分析

本文结合MSP430系列微处理器,详细论述了通过控制改变MCU的时钟频率来降低功耗的设计方法。

本文引用地址://www.cazqn.com/article/171370.htm1 功耗产生的原因

在CMOS电路中,功耗损失主要包括静态功耗损失和动态功耗损失两部分。其中静态功耗主要是由反偏PN结的漏电流和晶体管的亚阈值电流引起的,其最主要的形式就是漏电损失。其实CMOS电路理论上不会有静电功耗损失,因为从供应电源到地面没有直接的路径,但实际上晶体管总会有漏电电流的出现,从而出现漏电损失。在0.18μm工艺水平之下,其在功耗中所占比重大约为5%~10%,一般可以忽略(但是随着工艺的提高,供电电压的降低,又使其所占比重逐渐上升)。这样,在CMOS电路中,动态功耗就成了这个系统功耗的主要组成部分,约占整体功耗的90%以上。定量地分析电路的动态功耗,可用以下公式表示:

其中:C为负载电容;VDD为电源电压;?琢为翻转几率,即每个时钟周期中发生的充放电周期个数;fCLK为时钟频率。从这个公式可以看到如何降低动态功耗从而降低整个CMOS电路的功耗。即可以减小翻转的负载电容,降低电源电压,减小节点的翻转几率,或者降低时钟频率。本文将主要围绕如何动态降低时钟频率实现低功耗设计。

2 动态时钟低功耗管理原理

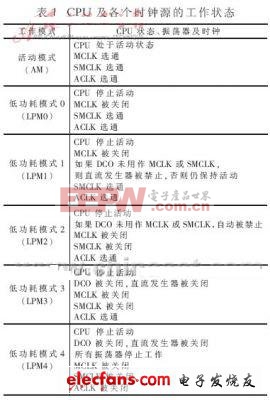

MCU系统设计是个很复杂的过程,在一些条件下可能会用到整个系统的所有硬件资源,但是在一些应用中可能只需要其中很少的一部分硬件资源;在某些应用中可能需要很高的时钟频率,而在其他应用中却可以工作在很低的工作频率中。例如:当任务量很大时,MCU满负荷工作,则需要较高的时钟频率,功耗较大;当任务量很小时,MCU负荷较轻,所需时钟频率较低,功耗就可以相应降低。动态配置系统的时钟频率就是以不牺牲系统的性能为前提,动态地管理系统的工作频率来降低MCU的功耗。

3 低功耗动态时钟实现

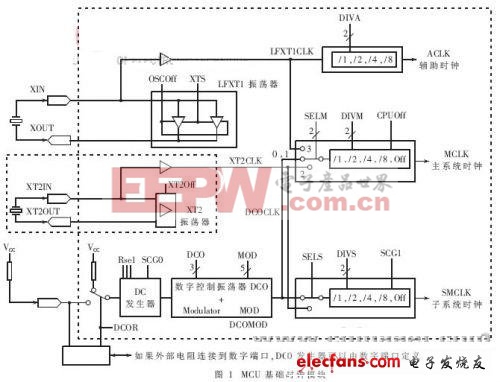

MSP430基础时钟模块包含以下3个时钟输入源。

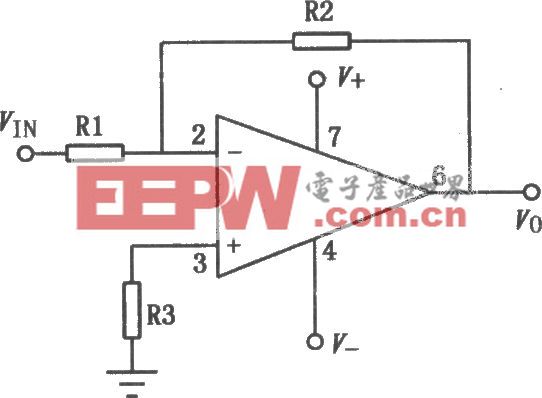

(1)LFXT1CLK 低频时钟源:由LFXT1振荡器产生(如图2所示)。通过软件将状态寄存器中OSCOff复位后,LFXT1开始工作,即系统采用低频工作。如果LFXT1CLK没有用作SMCLK或MCLK信号,则可以用软件将OSCOff置位,禁止LFXT1工作。

(2)XT2CLK高频时钟源:由XT2振荡器产生。它产生时钟信号XT2CLK,其工作特性与LFXT1振荡器工作在高频模式时类似。可简单地通过软件设置XT2振荡器是否工作,当XT2CLK没有用作SMCLK或MCLK信号时,关闭XT2,选择其他时钟源。

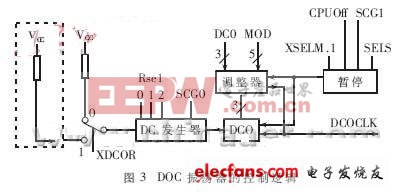

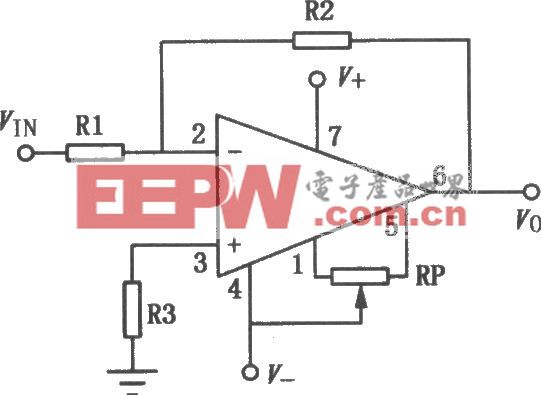

(3)DCOCLK 数字控制RC振荡器。由集成在时钟模块中的DCO振荡器产生。DCO振荡器是一个RC振荡器,频率可以通过软件调节,其控制逻辑如图3所示。当振荡器LFXT1、XT2被禁止或失效时,DCO振荡器被自动选作MCLK的时钟源。因此由振荡器失效引起的系统中断请求可以得到响应,甚至在CPU关闭的情况下也能得到处理。

评论