采用低成本FPGA构建IP监视摄像系统

IP监视摄像机参考设计

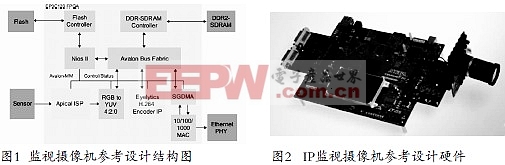

本文引用地址://www.cazqn.com/article/142476.htm图1所示为IP监视摄像机参考设计的顶层结构图和硬件,它主要面向新一代HD(>1MP)WDR传感器。IP监视摄像机参考设计结合了Altera以及多家合作伙伴的硬件和软件知识产权。

图2显示了参考设计的硬件平台,基于Cyclone III EP3C120开发板。Aptina WDR传感器像素数据被送入Apical的图像传感器流水线(ISP)。输出数据是YUV 4:2:0格式,写入到外部DDR2 SDRAM的帧缓冲中,它使用了Altera视频和图像处理(VIP)套装提供的组件。然后,使用EyeLytics提供的内核,以H.264格式对视频数据进行编码,支持(在这一应用中)3级基线/主要类视频流,通过以太网在远程主机上观看。散射收集直接存储器访问(SGDMA)控制器支持Altera三速以太网(TSE)MegaCore功能,将编码后的视频流通过以太网传送到远程客户端。

宽动态范围传感器

Aptina MT9M033是0.33" 720p60 WDR CMOS传感器,主要用于监视摄像机市场。传感器和镜头组合安装在“顶板”上,通过I/O转换板将其连接至Cyclone III EP3C120开发板。

图像传感器流水线

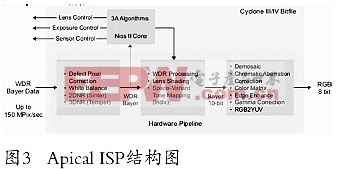

CMOS WDR传感器没有片内图像流水线处理功能,以RAW/Bayer格式输出图像数据,每像素为20比特。可以采用下式来计算传感器输出的大量原始数据:20比特/像素x(1280x720)像素/帧x60帧/s=>1Gbit/s。由于数据量过大,因此很难将新一代WDR传感器连接至监视解决方案中经常使用的ASSP。因此,FPGA是高效处理数据的理想选择。Apical的ISP(图3)包括以下功能:

● 去除热点像素,抑制噪声(提供空间和时域IP内核)。

● 使用Apical获奖的专利Iridix IP内核实现单位像素高级色调映射功能

● 高级去马赛克和颜色校正

fpga相关文章:fpga是什么

评论