一种基于FPGA的线阵CCD瞬态光谱信息采集系统设计

系统结构

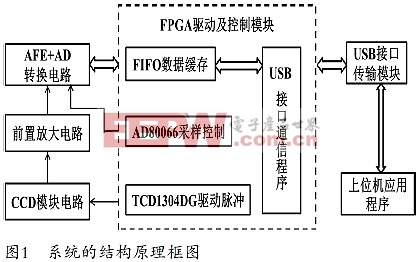

本文引用地址://www.cazqn.com/article/142474.htm系统的结构原理框图,如图1所示。系统主要包括CCD数据采集模块电路、输出信号前置放大电路、带模拟前端的AD转换电路、FPGA驱动及控制电路和USB接口电路等五部分。

系统上电后,上位机程序通过USB设备向FPGA发送控制命令,USB设备在该命令控制下完成对FPGA数据采集参数的初始化设置。FPGA根据初始化后的采集参数,产生相对应的TCD1304DG驱动时序,使之在该驱动时序的严格控制下工作。CCD采集模块输出的模拟信号经过前置放大电路处理后,进入专用视频信号处理器AD80066完成模拟前端处理和A/D数据转换,由FPGA片上高速FIFO实现数据缓存,然后通过USB接口将数据从FIFO中读出,传输给上位机以进行后期数据分析和处理。

系统的硬件构成

FPGA驱动及控制模块

本系统采用Xilinx公司Spartan-3系列的XC3S1000芯片,它具有很高性价比和丰富的逻辑资源,能满足采集系统的要求。FPGA作为该数据采集系统的控制核心,主要用来产生TCD1304DG的驱动时序、控制AD80066完成数据采样、合理配置内部FIFO用于缓存数据、通过USB接口通信模块将数据正确地传输到上位机中。

CCD模块电路

系统采用TCD1304DG作为感光元件,它是一款高灵敏度、低暗电流噪声、宽动态范围的线阵CCD器件。内部集成有驱动电路、采样保持电路,尤其是电子快门功能更便于探测爆轰之类的瞬时事件。TCD1304DG传感器工作时需要3路驱动时钟,包括转移脉冲SH、光积分控制脉冲 ICG 和主时钟脉冲M。通过对TCD1304DG的时序分析,在本设计中采用Verilog HDL语言进行编程,以完成TCD1304DG的驱动时序脉冲设计。

由于光积分时间的长短与CCD器件输出信号的强弱有关,选择合适的光积分时间将关系到CCD输出信号的质量。因此,本设计中采用了在FPGA内部控制线阵CCD光积分时间,实现曝光时间的自动控制。启动CCD的电子快门功能调节时,最小的曝光时间将达到10ms。

模拟信号相关文章:什么是模拟信号

fpga相关文章:fpga是什么

脉冲点火器相关文章:脉冲点火器原理

评论