使用LX9开发板对兼容ARM9处理器的开源软核进行Dhrystone Benchmark测试(上)

LX9开发板由安富利设计生产,体积小,便于携带。一端是普通的USB接口,可以插入笔记本或台式机,用ISE编程,下载到FPGA上。另外,为了便于调试,在另外一端也配备了USB的Type B接口,通过连接线,连到电脑后,可以实现USB转串口的功能。所以,笔者现在的开发就是通过在两个连接线把这块开发板与电脑的两个USB串口连接起来,一端是用来FPGA编程的,一端是串口调试的。接下来,笔者想与读者分享下如何使用这款兼容ARM9处理器的CPU内核进行Dhrystone Benchmark的测试。

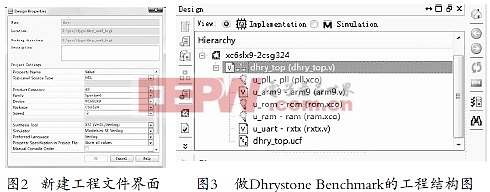

本文引用地址://www.cazqn.com/article/142463.htm首先,针对Spartan 6 LX9这块开发板新建FPGA project,须在Family中选择Spartan 6,在Device中选择XC6SLX9,在Package中选择CSG324,在Speed中选择-2,如图2所示。

新建工程后,我们就可以增加顶层文件,以及各种设计文件。下面是笔者做Dhrystone Benchmark的工程结构图。如图3所示,这个工程采用的是XC6SLX9-2CSG324,完全符合开发板中的FPGA设定。它有一个顶层文件: dhry_top(dhry_top.v),这个顶层文件涵盖了几个基本模块。这些基本模块有:u_pll模块(负责生成时钟);u_arm9模块:这就是兼容ARM9处理器内核;u_rom模块:存储处理器运行指令的ROM;u_ram模块:处理器运行需要的RAM;u_uart模块:一个简单的串口生成模块;dhry_top.ucf:整个工程的管脚约束文件。

首先介绍u_arm9-arm9(arm9.v),这是笔者设计的兼容ARM9处理器的CPU内核。它设计简单,易于集成到自己的设计当中,下表是它的接口列表。

为了让它工作起来,必须为它配备ROM提供执行的指令,配备RAM提供运行的空间。下面是它的简单的ROM和RAM模型。

这两个模型非常简单,容易采用FPGA内部的Block RAM来实现。ISE为我们准备了非常好的生成IP的工具——CORE Generator,只要我们选择Project-> New Source即可调出下面的界面。选择IP(CORE Generator & Architecture Wizard),可以生成本次Dhrystone Benchmark测试需要的三个IP: PLL、ROM、RAM。

具体的生成过程,大家可以自己摸索。下面通过顶层dhry_top.v来看看,这三个IP和uart模块是如何合并一起实现Dhrystone Benchmark测试的。

网线测试仪相关文章:网线测试仪原理

评论