BCD格式实时时钟的状态机逻辑

引言

本文引用地址://www.cazqn.com/article/142451.htm开发实时时钟(RTC)软件时,需要首先理解时钟核心逻辑的定义。我们通常对时钟和日历的工作原理有一个基本的认识,本文则深入分析了芯片在装载了不正确或不合法的内容时可能产生的后果。

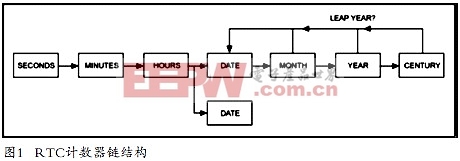

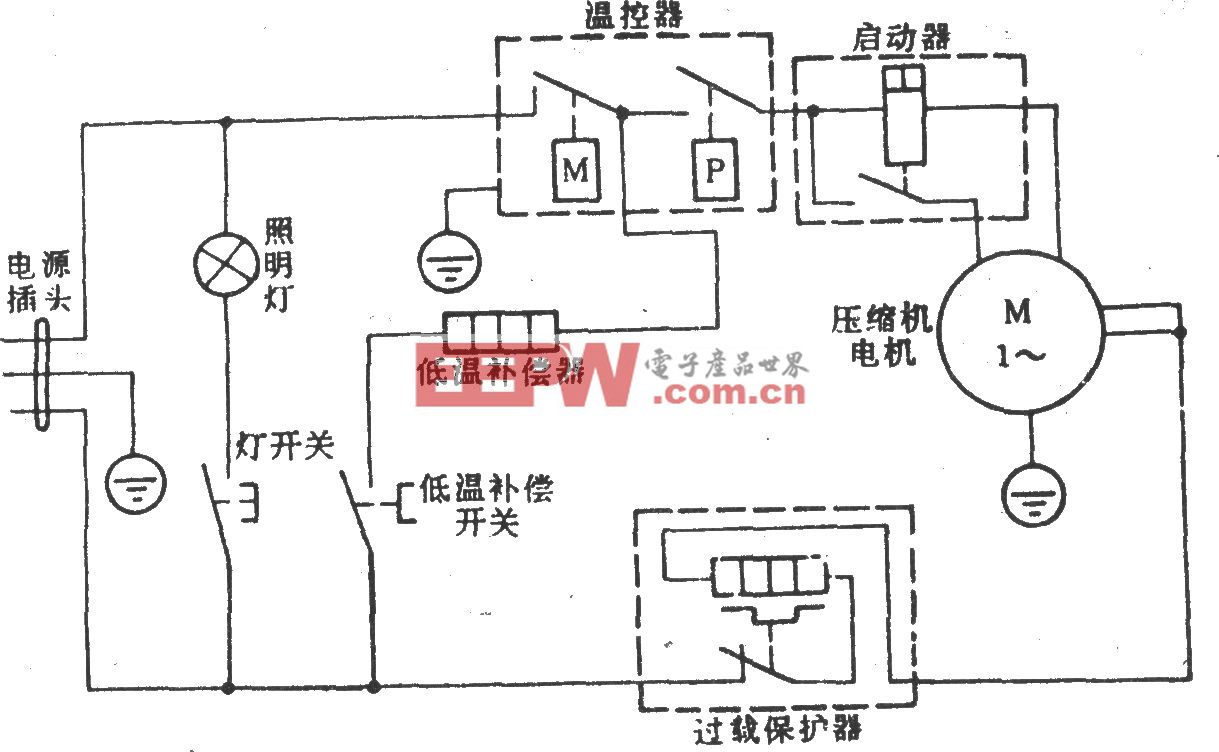

Maxim的多数BCD码RTC(例如DS12885和DS1302)内部都带有基本的实时时钟计数器链,如图1所示。

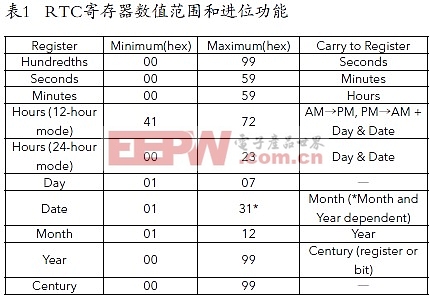

每个计数器寄存器具有确定的最小值和最大值,大多数寄存器在初始上电时预设为相应的最小值。作为计时功能,如果秒计数达到其最大值时,在下一个时钟到来时,进位至分钟寄存器,秒计数则返回最小值。同样,分钟进位至小时,小时进位至日期、星期寄存器,日期进位至月寄存器,月进位至年寄存器;必要时,随着年计数值的递增,将进位至世纪寄存器。表1列出了相应寄存器及其对应的有效值。

有些计数器可能包括“百分之一秒”寄存器(秒的前一位)和世纪标识位。

寄存器说明

对于每个寄存器,常规逻辑是从最小值到最大值递增的BCD计数,然后返回至最小值,并向下一级寄存器进位。例如,30天月份的日期寄存器BCD计数为:01h...09h、10h...19h、20h...29h、30h,然后返回01h。

Maxim实时时钟不检查用户在工作期间装载的数值,当装载错误的数据后,结果取决于具体器件及实际使用的寄存器。不合逻辑的时间和日期可能造成不确定的操作。

尘埃粒子计数器相关文章:尘埃粒子计数器原理

评论