基于Xilinx Spartan-6的高速接口设计

随着网络带宽的不断增加和数据率的不断提高,单端互联的方式由于噪声等的影响已经不能满足设计的要求。在高速数据通信系统中,由于LVDS(低压差分信号)有着良好的抗干扰能力而被广泛使用。然而由于许多MCU和DSP不支持LVDS标准的信号而使得接口设计复杂且难于调试。本设计模块采用Xilinx FPGA进行高速接口设计,电路简单,调试方便,且在某医疗器械中得到了应用。

本文引用地址://www.cazqn.com/article/142403.htmLVDS是美国国家半导体公司(编者注:2011年被TI收购)为了克服传统数据传送模式功耗大、抗干扰能力差而提出的一种新的接口标准,LVDS又由于参考电压的不同可分为: LVDS_25, LVDS_18, LVDS_33。且为了保证信号的完整性,LVDS信号通常需要在传输线上添加100欧姆的匹配电阻。

在同步设计的过程中,我们通常可以将时钟同步的方式分为三种:系统同步方式,源同步方式和嵌入式时钟同步方式。系统同步方式通常是指由一个时钟源产生时钟并连接到多个需要同步的元件。在高速通信的过程中,系统同步方式会由于时钟的抖动和偏斜,时钟传送的延迟等的影响而导致系统的时间裕留量的减少,从而导致系统无法工作。在高速通信过程中,我们通常采用源同步方式和嵌入式同步方式,嵌入式同步方式是通过特殊的编码将系统的时钟嵌入到需要传送的数据当中,系统接收到该组数据以后再通过相应的解码方式将时钟提取出来用于系统的同步。嵌入式同步方式目前在高速数据通信中得到了广泛的应用,如:ROCKET IO,PCIE等。

源同步方式是指系统的同步时钟是随需要接收的数据一起发送过来,而不是系统自身产生。所以源同步方式的信号通常有两对数据线:一对用于传送数据,一对用于传送时钟。源同步的方式通常能达到1Gbit以上的数据传送,因此源同步方式在高速数据通信中得到了较广泛的应用。

本模块采用Xilinx Spartan-6 LX45T接收以源同步方式发送过来的多路数据率为600Mbit/s、随路时钟为60MHz的信号,并与之通信。

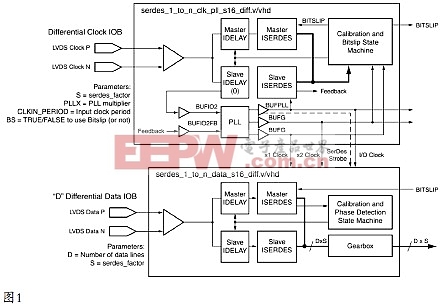

由Xilinx SerDes高速收发的原理可知,在此模块中我们应当对高速的数据进行1:10的串并转换,Xilinx提供SerDes原语进行串并转换,并提供了一系列的参考设计,具体可从官网下载文档XAPP1064。其中SerDes 原理可以大致概括如下:I/O从外部接收到两对数据以后(分别为时钟信号和数据信号):其中一对源同步时钟信号(在此我将它称之为 :TXCLK)通过IBUFGDS差分缓冲,变成单端时钟信号,将该时钟反相以后输入到 IODELAY原语进行时钟的延迟,其中时钟的延迟由bitslib和一个状态机进行控制,延迟的目的是使数据恰好能在时钟的正中间进行采集,经过延迟控制以后的时钟通过PLL和BUFPLL等进行处理,通过BUFG和BUFPLL以后有3或4个时钟信号提供给数据部分,1.提供给I/O的高速时钟(IOCLK);2.内部的并行的慢时钟(X1和X2);3.用于同步的脉冲(SerDes STROB)。 其中的一对数据信号(我们称其为TX),TX接收到发送端发送的数据以后,同样经过IODELAY和SerDes等的一系列处理,并由BITSLIP控制每个数据链的延迟,使得数据最终能和时钟的边沿对齐,TX进行数据转换的时钟都是由TXCLK经过处理后得到的。

数据的流程大致是这样的(注:笔者只是将它进行了一些简单的概括,更详细的介绍可以参考官网的一些资料):图1是我从官方下载的一个图片,可以较清晰的概括SerDes接收原理:

评论