基于Xilinx ISE的DDR SDRAM控制器的设计与实现

在高速信号处理系统中,需要缓存高速、大量的数据,存储器的选择与应用已成为系统实现的关键所在。DDR SDRAM是一种高速CMOS、动态随机访问存储器,它采用双倍数据速率结构来完成高速操作。DDR SDRAM一个时钟周期只能传输一个数据位宽的数据,因此在相同的数据总线宽度和工作频率下,DDR SDRAM的总线带宽比DDR SDRAM的总线带宽提高了一倍。

本文引用地址://www.cazqn.com/article/128748.htmDDR SDRAM控制器工作原理

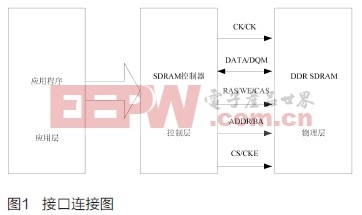

DDR SDRAM也是利用内部电容的电荷来记忆数据信息的,但电容的电荷会随着时间而泄露,所以要在数据信息变得难以辨认之前完成数据刷新(更新),也即将数据读出(但并不送到芯片管脚上)再写入,其一般是周期性的,整个存储器进行一次刷新的时间间隔为刷新周期。在刷新期间,不允许进行数据的读写操作。SDRAM的存储体是按照行列组织的二维矩阵,而刷新操作按行进行,每次对一行的数据同时读出、放大、整形和再写入。根据标准规定,DDR SDRAM的每一行都必须在64ms以内刷新一次。DDR SDRAM有自动刷新和自刷新两种刷新模式,且在每次突发读取时,都会自动预充电。DDR SDRAM芯片在上电后必须由一个初始化操作来配置DDR SDRAM的模式寄存器,模式寄存器的设置决定了DDR SDRAM的刷新模式。系统上电复位,SDRAM进入持续约200ms的初始化阶段之后,首先利用PCH指令对1个或4个BANK进行预充电,然后利用REF指令进行8次自动刷新,最后利用MRS指令配置DDR SDRAM进入所需工作模式,至此初始化阶段完成。其后进行数据存取操作,首先利用ACT命令打开一行(也称行有效),然后利用RD或WR命令进行单个读写或突发读写,一行完成要用PCH指令关闭该行,开始下一行数据存取操作依次循环,直至完成所有工工作。BANK激活命令后必须等待大于tCRD(SDRAM的RAS到CAS的延迟指标)时间后,发出写命令。CL(CAS潜伏期)个工作时钟,要向SDRAM发出预充值命令(PRECHARGE)命令,关闭已激活页。等待tRP时间关闭已激活页。SDRAM的基本写操作也需要控制线和地址线相配合发出一系列命令完成。先发出激活命令(ACTIVE),并锁存相应BANK地址(BA0,BA1)和行地址(A0~A12给出)BANK激活命令必须大于tRCD的时间后,发出写命令字写命令可以立即写入,需写入数据据依次送到DQ(数据线)上。在最后一个数据写入后延迟tWR时间。发出预充值命令,关闭已激活页。等待tRP时间后,可以展开下一次操作。写操作分为突发写和非突发写两种。突发长度同读操作。写操作控制时序如图1所示,读操作所等待的时钟个数由tRCD、tRP、tWR的最小值和工作周期决定。

存储器相关文章:存储器原理

电荷放大器相关文章:电荷放大器原理

评论