基于Virtex-4的DCM动态重配置设计

DCM概述

本文引用地址://www.cazqn.com/article/128746.htmVirtex-4系列FPGA是Xilinx公司推出的新一代大容量、高性能的FPGA。在Virtex-4系列FPGA内部最多集成了20个时钟管理器DCM模块,DCM提供了一个完整的可以供片内和片外使用的时钟发生器。DCM使用完全数字延迟线技术,允许高精度地控制时钟的相位和频率;使用完全的数字反馈系统,可以动态补偿由于温度和电压偏移引起的时钟相位和频率的偏差。DCM主要具有以下四个基本功能:数字时钟同步、数字频率合成、数字相位移动、动态重配置。

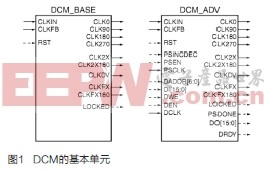

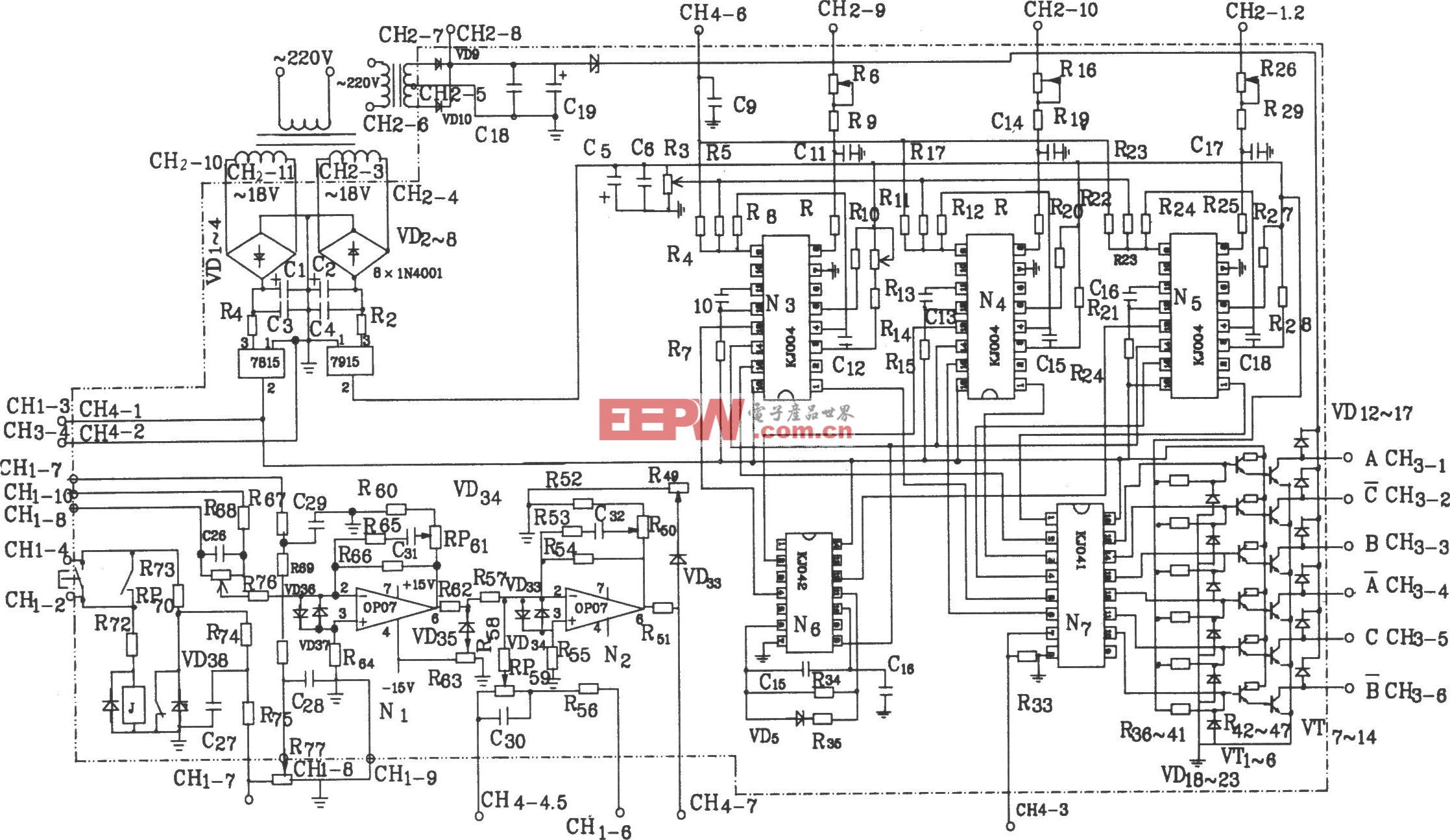

Virtex-4的DCM基本单元分为DCM_BASE和DCM_ADV两种,如图1所示,而DCM_ADV具有时钟动态重配置功能。

DCM_BASE基本单元包含常用的DCM基本功能,简化了用户接口。使用DCM_BASE,可以完成对时钟去歪斜、进行频率合成和固定相移的功能。

DCM_ADV基本单元除包含DCM_BASE中的所有DCM功能和可用端口之外,还包含具有动态重配置功能的端口。DCM_ADV基本单元是DCM_BASE基本单元的扩展。DCM_ADV包括所有DCM功能,包括时钟去歪斜、频率合成、固定或可变相移以及动态重配置。

DCM动态重配置的设计和实现

通过DCM的一组数据和地址总线,在不必重新配置器件的其他部分的情况下,改变DCM的属性。用于动态重配置DCM功能的引脚有:输入引脚DADDR[6:0],DI[15:0],DWE,DEN和DCLK;输出引脚DO[15:0]和DRDY。动态重配置可以根据目前的配置设定实现修改DCM的属性,改变其相移、倍频系数(M)或分频系数(D)。

评论