IP 授权

简介

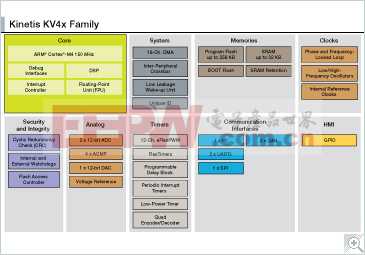

本文引用地址://www.cazqn.com/article/125596.htm文献[1]使我们在如下方面有了一个很好的了解:芯片里什么是主要电源消耗者以及如何克服。大部分动态功率消耗相关技术可以用寄存器传输语言(RTL)捕获或在合成脚本中控制。直到最近,关闭设计中某些部件电源的相关技术成为可能,仅通过把设计与特殊技术捆绑实现。一种常用的方式是hand-instantiate技术,是专门的功率控制元素。有争议的是,这种设计开发缓慢并容易出错。验证方法将涉及到门级或晶体管级模拟仿真,这很费时。缺点是需要了解语言开发,要用到CAD (计算机辅助设计)工具进行仿真和合成。本文的目的是对如下进行初步描述:电源控制需要做哪些事情,以及UPF如何使用软件IP处理。

电源控制所需的操作

为了实现低功率消耗,设计人员需要特殊的电源控制单元。电源控制的目的可能是:(a)使模块工作在不同的供电电压,时序要求严格的模块工作在较高电压下,(b)打开/关闭整个模块。

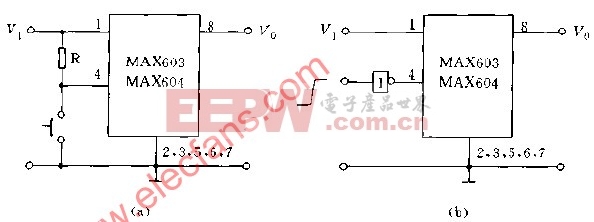

使模块工作在不同的供电电压需要使用电平移位器。

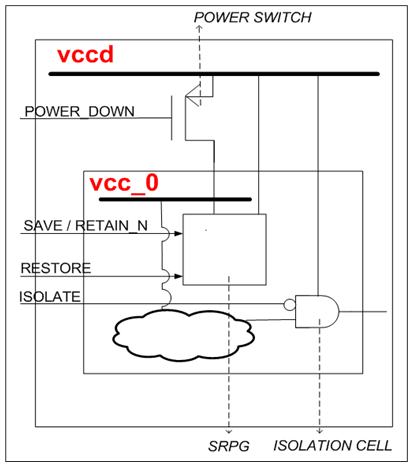

处理关闭模块电源时必须考虑到的关键元素是

a. 隔离单元:在正常的工作模式下,当模块没有关闭电源时,隔离单元只需要使逻辑值通过。当模块关闭电源时,隔离单元确保输出捕捉到一个已知逻辑值。逻辑值可以为“0”,' 1 '或最近的状态。

b. 电源状态保持门(SRPG): SRPG是当设为SAVE时,用来保持影子寄存器中寄存器内容的备份。当寄存器上电时,我们保持其值,设为RESTORE。影子寄存器备份的内容返回到主寄存器

c. 电源开关:这些是打开/关闭电源的单元。要注意,这些开关必须精密加工,避免多余的“IR”丢掉。

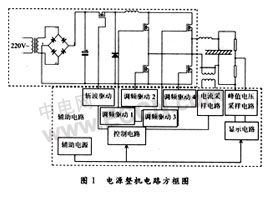

图1 电源控制基本组成

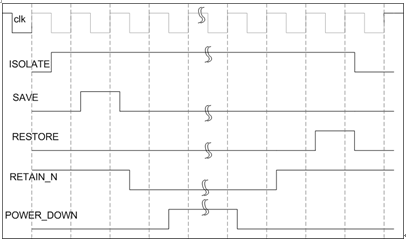

图2所示为电源控制的相关控制信号。请注意,“_N”后缀的信号为低有效。

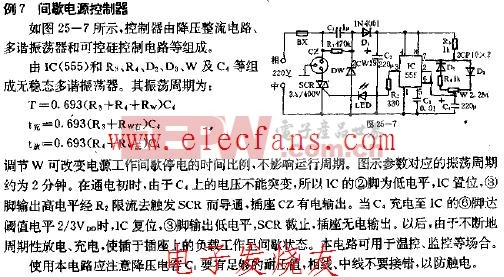

电源关闭时序必须按照以下步骤:(i) 需要关闭电源的模块必须要先隔离,这样相邻模块仍能收到有效的数字信号,(ii)设置SAVE信号,这样SRPG为保持模式,(iii)这时,所有连续和组合单元都处于接受关闭电源的状态。这时候POWER_DOWN就有效了。

电源上电时序要遵循下面步骤:(i) 禁用 POWER_DOWN, (ii) 禁用复位,有一个效果的上电复位,(iii) 当RESTORE 信号有效时,SRPG复制影子寄存器内容到主寄存器,(iv)允许隔离单元传输正常值。

RETAIN_N可以用SAVE 和 RESTORE信号来代替。

图2 电源控制信号时序

UPF:电源控制的实现

UPF文件可以使用一串命令执行电源供电规格。UPF提供的命令细节可在参考文献[2]中找到。可以为一个特定的软件IP(其捕捉整个电源事件)创建一个单一的文件。从而文件由仿真和合成工具创建。请注意,UPF流不需要RTL任何方式的改变。

UPF文件可以划分两个部分。一部分捕获供电分布网络。供电网络的主要因素包括:(i)功率域,(ii)电源端口,是特定功率域的一部分,(iii)从这些端口的供电网络设计元素在IP中。第二部分包括电源策略,例如隔离、保持、电位平移和电源状态。图3和图5分别对这两个部分进行了举例说明。请注意,我们认为电源开关属于前一部分,因为它为供电网络定义了端口。

图3 UPF示例:设置

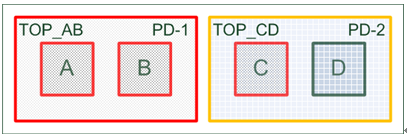

功率域是一个或多个设计元素的逻辑分组。功率域创建的逻辑层次称为功率域范围。所以,在图4中,PD-1适用范围是TOP_AB,PD-2适用范围是TOP_CD。有这种可能,即使C在TOP_CD,它也可能想要在PD-1操作。在这种情况下,可以说C在PD-1拓展范围,但在PD-2范围。

图4 功率域

图3需要注意, vccd跨越 了“默认”和“VCC_0” 功率域,但vcc_0网络只定义了功率域”VCC_0”。这是因为vccd为持续供电网络,其为SRPG供电。这是由选择”-retention_power_net vccd”到“set_retention”命令来实现的,如图5所示。

图5 UPF例程:保持、隔离和电源状态

UPF文件的一个重要方面是创建电源状态表(PST)。PST可以在一个设计中定义所有合法的和非法的电源状态。在图5所示的例程中,S1和S2代表PST的合法元素。从例子中PST定义可以推理,不可以选择关闭vccd,但vcc_0可开启或关闭。

结论

UPF已成为一个电源规范语言,大多数CAD工具现在已经可以识别它。它提供了一系列有用的命令,设计人员可以用来捕获电源意图。低电平设计元素(例如:SRPG、隔离单元,电平移位器和电源开关)不再需要在RTL中手动完成电源命令代码。设计可以以RTL、UPF和时序约束集合形式捕捉。这可以方便各种技术关键性能因素(如电源、区域和速度)能合理控制。

声明

感谢Anand Moghe 和Deepak N K为本文的贡献。

参考文献

[1] IEEE JOURNAL OF SOLID-STATE CIRCUITS.。27卷, 1992年4月4日。低功耗CMOS数字设计。作者:Anantha P. Chandrakasan, Samuel Sheng, 和 Robert W. Brodersen.

[2] “Accellera” Unified Power Format (UPF)标准,1.0版本。

http://www.unifiedpowerformat.com/imagses/UPF.v1.0_Standard.pdf

[3] Michael Keating et al“片上系统设计低功率设计手册”

评论