为什么会有这么多电平标准?

电平标准的多样性主要源于以下几个原因:

本文引用地址://www.cazqn.com/article/202408/461609.htm历史和兼容性: 不同国家和地区在不同历史时期制定了各自的电平标准,这些标准反映了当时的技术水平和需求。随着时间的推移,为了保持兼容性和延续性,许多旧的标准被保留下来并与新的标准共存。

应用需求: 不同的应用场景对电平有不同的要求。例如,工业控制系统、音频设备、通信系统和计算机网络对信号电平的要求各不相同,导致了各种专门化的电平标准的出现。

技术限制: 不同的技术在实现过程中有其自身的限制和最佳操作条件。例如,早期的电子设备和现代数字设备对电平的要求和处理能力差别很大,这导致了不同的电平标准。

标准化组织: 世界上存在多个标准化组织,如国际电工委员会(IEC)、国际标准化组织(ISO)、美国国家标准学会(ANSI)等,它们根据各自的区域和行业需求制定标准。这些组织有时会制定不同的电平标准,以满足特定地区或行业的需求。

安全性和可靠性: 不同的应用对安全性和可靠性的要求不同。例如,电力系统需要非常严格的电平标准来保证安全,而消费电子产品可能更注重成本和易用性,因此在电平标准上会有所不同。

信号速率和半导体工艺的发展: 随着信号处理和传输速率的不断提高,半导体工艺也在不断进步。这种进步导致了信号摆幅(即电压摆幅)的不断减小,以适应更高的速率和更小的工艺节点。例如,在现代高速内存接口如DDR(双倍数据速率)技术中,电压标准已经从最早的DDR的2.5V降到DDR4的1.2V,甚至更低的DDR5的1.1V。这种变化主要有以下几个原因:

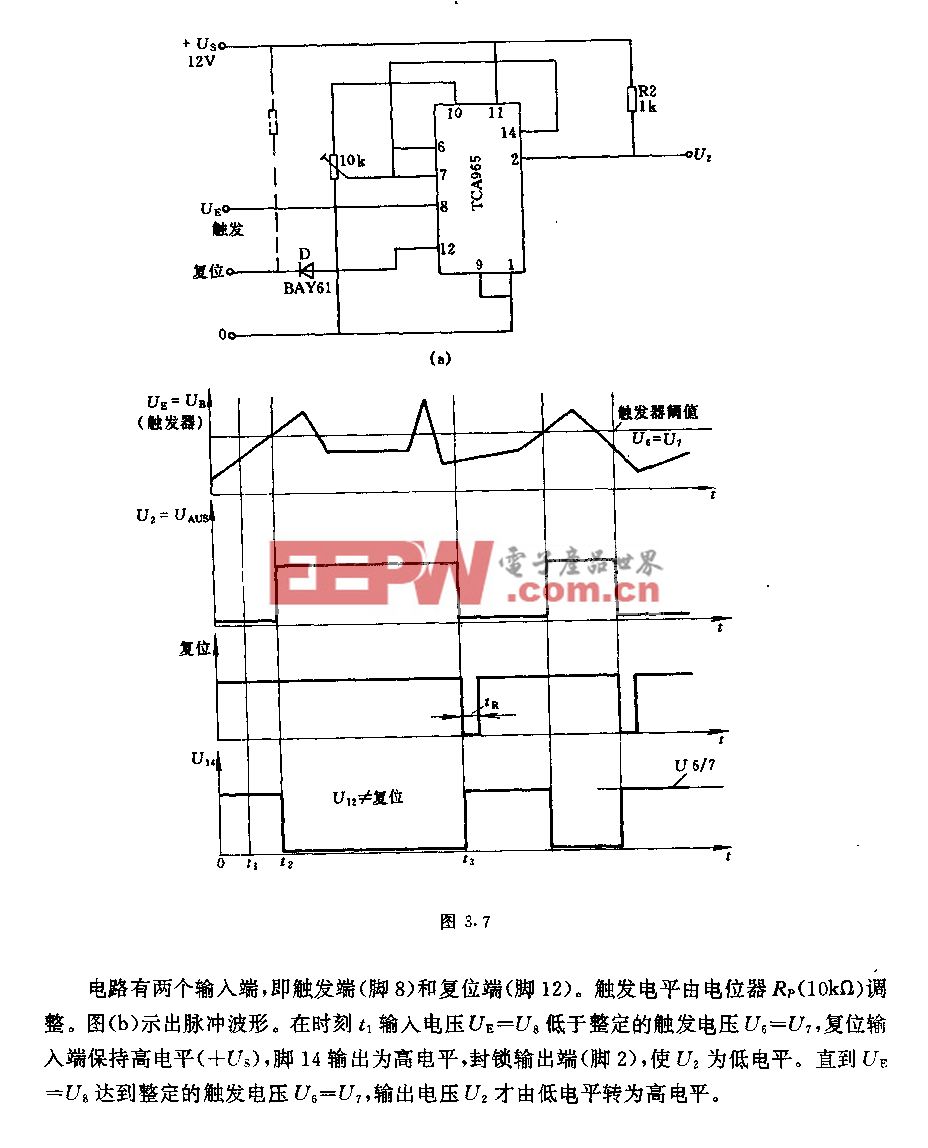

逻辑电平的一些概念

要了解逻辑电平的内容,首先要知道以下几个概念的含义:

1:输入高电平(VIH):保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于 VIH 时,则认为输入电平为高电平。

2:输入低电平(VIL):保证逻辑门的输入为低电平时所允许的最大输入低电平,当输入电平低于 VIL 时,则认为输入电平为低电平。

3:输出高电平(VOH):保证逻辑门的输出为高电平时的输出电平的最小值,逻辑门的输出为高电平时的电平值都必须大于此 VOH。

4:输出低电平(VOL):保证逻辑门的输出为低电平时的输出电平的最大值,逻辑门的输出为低电平时的电平值都必须小于此 VOL。

5:阈值电平(VT):数字电路芯片都存在一个阈值电平,就是电路刚刚勉强能翻转时的电平。它是一个界于 VIL、VIH 之间的电压值,对于 CMOS 电路的阈值电平,基本上是二分之一的电源电压值,但要保证稳定的输出,则必须要求输入高电平> VIH,输入低电平<VIL,而如果输入电平在阈值上下,也就是 VIL~VIH 这个区域,电路的输出会处于不稳定状态。

对于一般的逻辑电平,以上参数的关系如下:

VOH > VIH > VT > VIL > VOL。

6:IOH:逻辑门输出为高电平时的负载电流(为拉电流)。

7:IOL:逻辑门输出为低电平时的负载电流(为灌电流)。

8:IIH:逻辑门输入为高电平时的电流(为灌电流)。

9:IIL:逻辑门输入为低电平时的电流(为拉电流)。

扇出能力也就是输出驱动能力,通常用驱动同类器件的数量来衡量。

TTL:扇出能力一般在 10 左右。

CMOS:静态时扇出能力达 1000 以上,但 CMOS 的交流(动态)扇出能力没有这样高,要根据工作频率和负载电容来考虑决定。

限制因素是输入信号上升时间:本身输出

电阻和下级输入电容形成积分电路影响输入信号的上升时间(输入信号从低电平上升到VIH min 所需时间),实际电路当中,尽量使被驱动输入端限制在 10 以内。

ECL:由于 ECL 的工作速度高,考虑到负载电容的影响, ECL 的扇出一般限制在10 以内。

门电路输出极在集成单元内不接负载电阻而直接引出作为输出端,这种形式的门称为开路门。开路的 TTL、 CMOS、 ECL 门分别称为集电极开路( OC)、漏极开路

( OD)、发射极开路( OE),使用时应审查是否接上拉电阻( OC、 OD 门)或下拉电阻

( OE 门),以及电阻阻值是否合适。对于集电极开路( OC)门,其上拉电阻阻值 RL 应

满足下面条件:

( 1):RL < ( VCC-VOH) /( n*IOH+m*IIH)

( 2):RL > ( VCC-VOL) /( IOL+m*IIL)

其中 n:线与的开路门数;m:被驱动的输入端数。

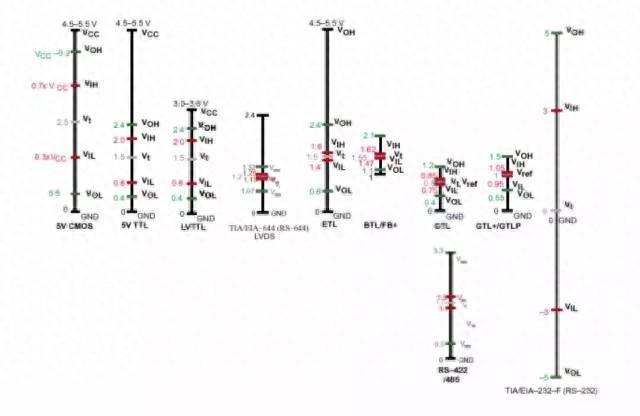

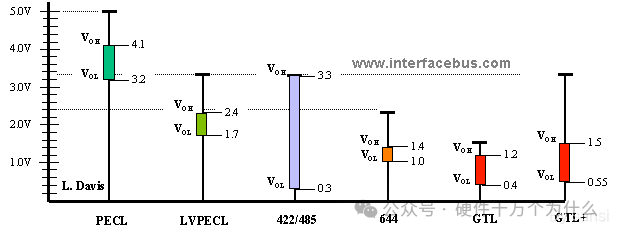

1.2:常用的逻辑电平

逻辑电平:有 TTL、 CMOS、 ECL、 PECL、 GTL;RS232、 RS422、 LVDS 等。

其中 TTL 和 CMOS 的逻辑电平按典型电压可分为四类: 5V 系列( 5V TTL 和 5VCMOS)、 3.3V 系列, 2.5V 系列和 1.8V 系列。

5V TTL 和 5V CMOS 逻辑电平是通用的逻辑电平。

3.3V 及以下的逻辑电平被称为低电压逻辑电平,常用的为 LVTTL 电平。低电压的逻辑电平还有 2.5V 和 1.8V 两种。

ECL/PECL 和 LVDS 是差分输入输出。

RS-422/485 和 RS-232 是串口的接口标准, RS-422/485 是差分输入输出, RS-232是单端输入输。

以下是一些常见的逻辑电平标准及其相关特性:

TTL (Transistor-Transistor Logic):

逻辑低(Low):0V - 0.8V

逻辑高(High):2V - 5V

电压范围:

供电电压: 通常为5V

特点: 广泛用于早期数字电路,易于使用,但功耗相对较高。

CMOS (Complementary Metal-Oxide-Semiconductor):

逻辑低(Low):0V - 1/3 Vcc

逻辑高(High):2/3 Vcc - Vcc

电压范围:

供电电压: 3.3V、5V,现代设备中也有1.8V、1.2V等

特点: 功耗低,输入阻抗高,适用于低功耗设计。

LVTTL (Low Voltage TTL):

逻辑低(Low):0V - 0.4V

逻辑高(High):2V - 3.3V

电压范围:

供电电压: 3.3V

特点: TTL的低电压版本,功耗较低。

LVCMOS (Low Voltage CMOS):

逻辑低(Low):0V - 0.2 Vcc

逻辑高(High):0.8 Vcc - Vcc

电压范围:

供电电压: 1.8V、2.5V、3.3V等

特点: 更低功耗,适用于现代低电压应用。

ECL (Emitter-Coupled Logic):

逻辑低(Low):-1.8V

逻辑高(High):-0.8V

电压范围:

供电电压: -5.2V

特点: 非常高的速度,但功耗较大,多用于高速应用。

PECL (Positive Emitter-Coupled Logic):

逻辑低(Low):Vcc - 1.7V

逻辑高(High):Vcc - 1.0V

电压范围:

供电电压: +5V或+3.3V

特点: ECL的正电源版本,高速,较高功耗。

LVDS (Low-Voltage Differential Signaling):

逻辑低(Low):电压差 < 0V

逻辑高(High):电压差 > 0V

电压范围:

供电电压: 3.3V,1.8V等

特点: 差分信号,低电压摆幅,低功耗,高速,抗干扰能力强。P

PCIe(Peripheral Component Interconnect Express)是一种高速串行计算机扩展总线标准,广泛用于计算机和服务器中连接外围设备。PCIe使用了以下几种电平标准:

LVDS(Low-Voltage Differential Signaling):

电平标准:PCIe采用LVDS来传输高速数据。LVDS使用差分信号来减少电磁干扰(EMI)和串扰,从而提高数据传输的可靠性。

电压范围:差分电压摆幅通常在250mV到450mV之间,这使得信号更加稳定和抗干扰。

CMOS(Complementary Metal-Oxide-Semiconductor):

电平标准:PCIe接口的控制信号和管理信号通常采用CMOS电平标准。

电压范围:这些信号的电压范围通常为1.2V、1.8V或3.3V,具体取决于使用的CMOS工艺节点。

HSTL (High-Speed Transceiver Logic):

逻辑低(Low):0V - 0.35V

逻辑高(High):0.65V - Vcc

电压范围:

供电电压: 1.5V、1.8V等

特点: 用于高速数据传输,适合于DDR存储器接口。

SSTL (Stub Series Terminated Logic):

逻辑低(Low):0V - 0.2Vcc

逻辑高(High):0.8Vcc - Vcc

电压范围:

供电电压: 1.8V、2.5V、3.3V等

特点: 用于高速存储器,如DDR SDRAM。

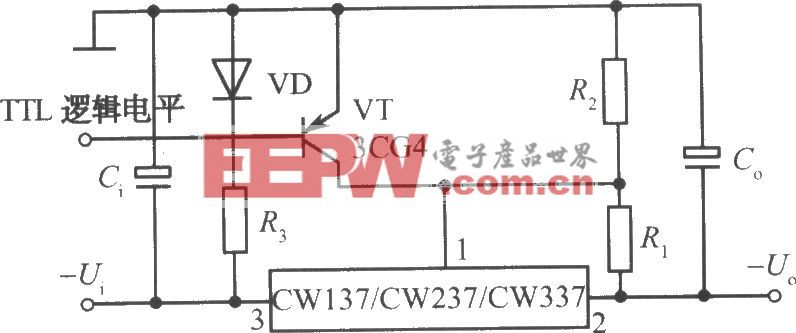

1.3开路门

门电路输出极在集成单元内不接负载电阻而直接引出作为输出端,这种形式的门称为开路门。开路的TTL、CMOS、ECL门分别称为集电极开路(OC)、漏极开路(OD)、发射极开路(OE),使用时应审查是否接上拉电阻(OC、OD门)或下拉电阻(OE门),以及电阻阻值是否合适。对于集电极开路(OC)门,其上拉电阻阻值RL应满足下面条件:

(1):RL < (VCC-Voh)/(n*Ioh+m*Iih) 拉电流尽可能大

(2):RL > (VCC-Vol) /(Iol+m*Iil) 灌电流尽可能小

其中n:线与的开路门数;m:被驱动的输入端数。

评论